CPLD Pojasnilo: Vodnik po programirljivi logični napravi

V dinamičnem svetu elektronskega oblikovanja kompleksne programirljive logične naprave (CPLD) izstopajo kot vsestranska orodja, brezhibno mešajo prilagodljivost, natančnost in učinkovitost.Te naprave so revolucionirale oblikovanje vezja z uvedbo programirljivih makro celic in prevladujoče matrike medsebojne povezave, kar omogoča ustvarjanje zapletenih logičnih funkcij z izjemno zanesljivostjo.Od njihovega začetka v osemdesetih do njihove ključne vloge v sodobnih panogah, kot so mreženje, avtomobilski in vesoljski, so CPLD -ji izkazali nujne za vas, da iščete tako prilagodljivost kot zmogljivost.Ta članek se kopa v potovanju CPLD -jev, njihovih značilnosti, praktičnih aplikacij in programskih metodologij, ki so temeljni kamen v digitalni logični zasnovi.Katalog

Pregled CPLD

Znotraj prevlade kompleksnih programirljivih logičnih naprav (CPLD) odkrije prefinjeno tapiserijo programirljivih logičnih makro celic, prepletenih skozi prevladujočo medsebojno povezovanje matriksa.Te makro celice (MC) in vhodne/izhodne (V/I) enotne črte omogočajo spretno oblikovanje tokokrogov in konfigurirate strukture za edinstvene funkcije.Za razliko od naprav, ki so zmedene zaradi njihovega zapletenega medsebojnega povezovalnega časa, CPLD uporabljajo nepremične kovinske žice.Ta značilnost jim daje dosledno in predvideno uro, zaradi česar so napovedi časovne razporeditve bolj zanesljive in natančne.

Potovanje in uporaba

V sedemdesetih letih prejšnjega stoletja so napovedali pojav programirljivih logičnih naprav (PLDS) in spodbudili premik k programabilnim makro enotam.Ta premik je uvedel dovolj prilagodljivosti oblikovanja in jih ločil od statičnih digitalnih vezij, čeprav je bila njihova uporabnost sprva omejena na enostavnejša vezja.Pojav CPLD-jev sredi osemdesetih je spremenil to pokrajino in utrl pot za zapletene modele vezja.Od takrat so se prepletali v tkanino industrij, kot so mreženje, avtomobilska elektronika, obdelava CNC in vesoljski sistemi.Lahko se spomnite na način, kako CPLD poenostavijo procese, ki so nekoč zahtevali natančno ročno delo, kar označuje izjemen preskok učinkovitosti.

Značilne lastnosti CPLDS

CPLD se ločijo s svojim prilagodljivim programiranjem, obsežno integracijo, hitro razvojnimi zmogljivostmi in široko uporabnostjo, skupaj z ekonomičnimi stroški proizvodnje.Apelirajo na tiste z minimalno izkušnjo strojne opreme, ki služijo kot zanesljivi in varni izdelki, ki ne potrebujejo izčrpnega testiranja.Kot dokaz njihove spretnosti v obsežnih modelih vezja imajo CPLD ključno vlogo pri razvoju prototipov in služijo vožnjam pod 10.000 enotami, kar predstavlja koristno pristojnost za vas.Spretnost, s katero se CPLD -ji prilagajajo razvijajočim se zahtevam projekta, jih pogosto zasluži in poudarja njihovo dejansko vsestranskost v dinamičnih okoljih.

Metode aplikacije

Ta integrirana vezja vam omogočajo, da podrobno opišete logične funkcije, prilagojene njihovim potrebam z uporabo shem in opisa strojne opreme na razvojnih platformah.Na primer, pri oblikovanju odzivniškega stroja so sheme in opisi strojne opreme pripravljeni in sestavljeni v računalniku.Z uporabo kabla za prenos se koda prenese v CPLD za programiranje v sistemu, ki obsega testiranje, odpravljanje težav in izboljšanje modelov.Uspešno izdelani modeli se nato množično proizvajajo s ponovitvijo čipov CPLD.V projektih, kot so semafonski sistemi, ponavljanje procesa oblikovanja postane nujno, podobno kot obnova hiše za obnovo njene novosti.Ta ponavljajoča se metodologija pogosto postavlja osnova za obvladovanje, povečanje tako spretnosti kot zaupanja.

Vodilne različice

Podjetja, kot so Altera, Lattice in Xilinx, so skozi leta razkrila vidne linije CPLD.Omembe vredni primeri vključujejo Altera's EPM7128S, Rešetke LC4128V, in Xilinx's XC95108 .Ti modeli so našli vidne vloge v različnih globalnih aplikacijah.Tisti, ki so imeli privilegij sodelovati s temi različnimi izdelki, pogosto opozarjajo na subtilne, a močne razlike, ki optimizirajo določene funkcionalnosti.To odraža postopek izbire, na katerega vplivajo posebne zahteve projekta, kjer ima vsaka varianta svojo edinstveno privlačnost.

Identifikacija in razvrstitev FPGA in CPLD

|

Vidik |

CPLD |

Fpga |

|

Logično oblikovanje vedenja |

Oblikujte logično vedenje z uporabo strukture izdelka.

Primeri: Serija rešetke ISPLSI, serija Xilinx XC9500, Altera Max7000S

serija, serija rešetka |

Oblikujte logično vedenje po metodi iskanja tabele.

Primeri: serija Xilinx Spartan, Altera Flex10K, serija ACEX1K |

|

Primernost |

Primerno za algoritme in kombinirano logiko, deluje

bolje z omejenimi sprožilci in bogatimi pogoji izdelka |

Primerno za zaporedno logiko, deluje bolje z

strukture, bogate s sprožilci |

|

Zamuda s časom |

Neprekinjena ožičevalna struktura zagotavlja enotno in

Predvidljive zamude v času |

Segmentirana struktura ožičenja vodi do nepredvidljivega časa

zamude |

|

Prilagodljivost programiranja |

Fiksna notranja vezja so spremenjena za programiranje.

Uporablja se logično programiranje na ravni bloka |

Notranje ožičenje je spremenjeno za programiranje.Logika

Programiranje na ravni vrat omogoča večjo prilagodljivost |

|

Integracija |

Nižja integracija v primerjavi s FPGA |

Višja integracija s bolj zapleteno strukturo ožičenja in

logična implementacija |

|

Enostavnost uporabe |

Lažje za uporabo s programiranjem prek E2Prom ali FastFlash.

Zunanji pomnilniški čip ni potreben |

Potrebuje zunanji pomnilnik za shranjevanje programiranja

informacije, ki vodijo do bolj zapletene uporabe |

|

Hitrost in predvidljivost |

Hitrejša hitrost in boljša predvidljivost časa zaradi

Zgrožena medsebojna povezava med logičnimi bloki |

Počasnejša hitrost in manj predvidljiv čas zaradi

Programiranje na ravni vrat in porazdeljeno medsebojno povezovanje |

|

Tehnologija programiranja |

Uporablja programiranje E2Prom ali Flash pomnilnik.Programiranje podatkov

se zadrži, ko je sistem izklopljen.Podpira programiranje na

programer ali v sistemu |

Na podlagi programiranja SRAM.Podatki o programiranju se izgubijo, ko

Sistem je izklopljen in ga je treba ponovno naložiti.Podpira dinamično

Konfiguracija |

|

Zaupnost |

Ponuja boljšo zaupnost |

Zagotavlja nižjo zaupnost |

|

Poraba energije |

Na splošno večja poraba energije, zlasti pri

višja integracija |

Nižja poraba energije v primerjavi s CPLD |

Programski jeziki CPLD

Analiza, kako so kompleksne programirljive logične naprave (CPLD) programirane, je temelj pri izdelavi vsestranskih strojnih rešitev.Zgodovinske metode programiranja CPLD so se opirale na diagrame lestev ali opis strojne opreme (HDLS), pri čemer prevladujejo Verilog HDL in VHDL.Izbrani jezik lahko oblikuje tako oblikovalsko strategijo kot operativno učinkovitost izvajanja.

• Verilog Hdl: Verilog HDL je negovan zaradi svojih preprostih sintakse in robustnih simulacijskih zmogljivosti, kar odraža metodologije, ki se uporabljajo v digitalni logični zasnovi.Njegova integracija z orodji za elektronsko oblikovanje (EDA) vam omogoča, da brezhibno izvajate sintezo in simulacijo.Opaženo je, da je C-podobna sintaksa Verilog znižala oviro za vstop za tiste s programskimi ozadji in pospešila pot od zasnove do uvajanja v širokem razponu industrijskih sektorjev.

• VHDL: VHDL ponuja bolj izpopolnjeno in izrazno možnost za programiranje HDL.Pogosto je izbira za projekte, ki zahtevajo natančno dokumentacijo in strogo preverjanje tipa, lastnosti, ki jih cenijo v vesoljski in obrambni industriji.Lahko opazite, da kljub potencialni zapletenosti VHDL v manjših projektih njegova disciplinirana struktura podpira ustvarjanje izjemno zanesljivih modelov, nujnost v okoljih, kjer prevladuje varnost.

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

NMOS tranzistorji: oblikovanje, delovanje in aplikacije

na 2024/12/29

Hitra Fourierjeva transformacija (FFT): revolucionarna digitalna obdelava signalov

na 2024/12/29

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/18 147765

-

USB-C pinout in funkcije

na 2000/04/18 111994

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/18 111351

-

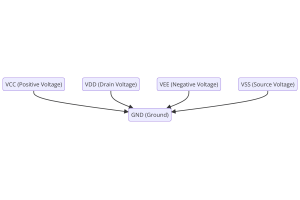

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/18 83751

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79548

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66949

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63094

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63028

-

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54094

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52175