Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

Analiza končne arhitekture računalniških procesorjev razkriva zapletenosti njihovega delovanja in zmogljivosti.Med najvplivnejšimi modeli procesorja so kompleksni računalnik z navodili (CISC) in znižane arhitekture računalniškega računalnika (RISC).Vsak ponuja edinstvene pristope k izvajanju navodil, učinkovitosti programiranja in oblikovanju strojne opreme.Ta članek raziskuje zapletenosti arhitekture CISC, s poudarkom na obsežnem naboru navodil, ki poenostavi programiranje, hkrati pa predstavlja izzive strojne opreme.Prav tako se kopa v racionalizirani pristop RISC, ki optimizira delovanje s poenostavljenim in učinkovitim naborom navodil.Nazadnje Post poudarja, kako sodobni procesorji vse bolj sprejemajo hibridne arhitekture in mešajo prednosti CISC in RISC, da bi zadovoljili različne računske potrebe.Katalog

Pregled CISC

Arhitektura računalniškega procesorja se osredotoča na izvajanje različnih navodil ali mikroinstrukcij, vsaka pa je zasnovana za izpolnjevanje posebnih nalog.Medtem ko lahko bolj celovit nabor pouka naredi programiranje za mikroprocesor bolj intuitivno, lahko uvede tudi potencialne ovire.Arhitektura Complex Instruction Set Comput (CISC) izstopa zaradi velike zbirke navodil, vključno z zapletenimi, ki poenostavijo programsko izkušnjo v primerjavi z alternativnimi arhitekturami.Vsaka naloga, ne glede na to, ali je preprosta ali zapletena, je seznanjena z edinstvenim navodilom, ki zmanjšuje potrebno količino kodiranja.Vendar lahko ta zapletena zasnova predstavlja opazne izzive pri razvoju CPU -ja in pripadajočega vezja kontrolne enote.

CISC -ovo arhitekturo odlikuje širok izbor mikroinstrukcij, ki olajšajo razvoj programa za procesor.Te mikroinstrukcije, ki so pogosto artikulirane v montažnem jeziku, nadomeščajo nekatere funkcije, ki jih je programska oprema tradicionalno ravnala s sistemi navodil na ravni strojne opreme.Ta premik ne samo osvetli delovno obremenitev za vas, ampak tudi omogoča hkratno izvajanje operacij na nizki ravni med vsakim navodilom, kar poveča skupno hitrost izvajanja računalnika.

Pogostost uporabe pouka znotraj sklopa CISC pouk prikazuje presenetljivo neravnovesje.Približno 20% navodil se običajno uporablja, kar predstavlja približno 80% celotne programske kode, preostalih 80% pa redko, kar prispeva k le 20% programiranja.To opazovanje odmeva s širšim načelom, ki ga opažamo na različnih področjih: majhen izbor orodij ali metod pogosto prinaša večino rezultatov.

Primerjava CISC in RISC

Arhitektura z zmanjšanim računalnikom (RISC) izstopa zaradi racionaliziranega nabora navodil, katerega namen je povečati učinkovitost procesorja.Ta zasnova pa zahteva bolj izpopolnjen pristop k zunanjim programiranjem.Z osredotočanjem na najpogosteje uporabljena preprosta navodila se RISC učinkovito izogne zapletom, ki pogosto spremljajo bolj zapletene ukaze.

• RISC Architecture standardizira dolžino pouka.

• Poenostavlja formate navodil, predvsem se zanaša na kontrolno logiko.

• Ta izbira oblikovanja odpravlja potrebo po krmiljenju mikrokode, kar ima za posledico hitrejše delovne hitrosti.

Izvor RISC -a je mogoče zaslediti do prelomne raziskave, ki jih je opravil John Cocke na IBM -u.Njegove ugotovitve so pokazale, da le približno 20% računalniških navodil predstavlja približno 80% računske delovne obremenitve.Ta vpogled ima veliko težo, kar kaže na to, da je z optimizacijo najpogosteje izvedenih navodil mogoče doseči obsežne izboljšave uspešnosti.Posledično sistemi RISC pogosto prekašajo kompleksne nastavitvene sisteme (CISC), ki se uskladijo z znanim načelom 80/20, ki sporoča razvoj arhitekture RISC.

Medtem ko se RISC ponaša z več prednosti, ne nadomešča v celoti CISC Architecture.Vsaka vrsta ima svoje različne prednosti, razlike med njimi pa so sčasoma postale manj izrazite.V sodobni praksi mnogi sodobni CPU vključujejo elemente tako RISC kot CISC, kar odraža naraščajoč trend hibridnih arhitektur.Na primer, CPU-ji ultra dolgega pouka (ULIW) ponazarjajo to mešanico in združujejo prednosti obeh arhitektur za izdelavo bolj prilagodljive procesne enote.Ta fuzija ne samo poveča zmogljivost, ampak tudi uvaja prožnost pri programiranju, kar omogoča širši obseg aplikacij.

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Square Quad Flat Paket (QFP) Tehnologija: Oblikovanje, aplikacije in izzivi

na 2024/12/30

Izbrisljive programirljive logične naprave (EPLDS): Vodnik po oblikovanju in aplikacijah

na 2024/12/30

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/18 147771

-

USB-C pinout in funkcije

na 2000/04/18 112007

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/18 111351

-

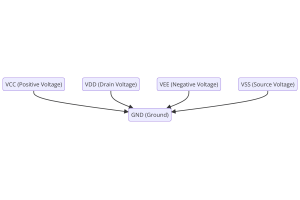

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/18 83768

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79565

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66960

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63098

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63040

-

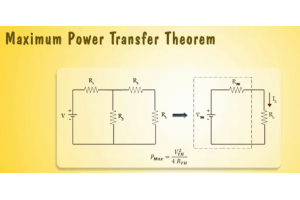

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54097

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52184