Celovit vodnik za testne steze: Orodja in tehnike za preverjanje digitalnega sistema

Ta priročnik raziskuje Testbenches, ključno orodje za validacijo programske opreme, ki simulira pogoje za testiranje vhodov in preverjanje izhodov.Testnike igrajo vlogo pri prepoznavanju napak zgodaj v razvoju in izboljšanju zanesljivosti programske opreme.Ta članek s praktičnimi primeri in vpogledi poudarja njihovo uporabo, tehnike in pomen pri gradnji močnih, učinkovitih digitalnih sistemov.Katalog

Vloga testnih pregledov pri validaciji digitalnega sistema

Testbench je komponenta v postopku validacije digitalnega sistema.To ni zgolj orodje za ustvarjanje vhodov in preverjanje izhodov, ampak je celovit okvir, ki simulira pogoje za oceno zanesljivosti, funkcionalnosti in vedenja digitalnih sistemov, preden so nameščeni na terenu.Z ustvarjanjem nadzorovanih okolij v sisteme stresnega testa s široko paleto vhodnih scenarijev vam testnike pomagajo prepoznati potencialne napake v oblikovanju že zgodaj v življenjskem ciklu razvoja, dolgo preden se sistem postavi v proizvodnjo.To zgodnje odkrivanje napak in ranljivosti je potrebno za zmanjšanje dragih napak, zagotavljanje skladnosti s specifikacijami uspešnosti in izboljšanje splošne zanesljivosti sistema.

Poleg preverjanja pravilnosti odzivov sistema igrajo tudi testne krmne vlogo pri ocenjevanju primerov, časovnih težav in mehanizmov za ravnanje z napakami, pri čemer zagotavljajo, da lahko sistem pravilno deluje tudi v ekstremnih ali nepričakovanih pogojih.Z avtomatiziranim testiranjem in simulacijo testnimi stenami prispevajo k višji kakovosti programske opreme, izboljšani zmogljivosti in krajših razvojnih ciklih, tako da omogočajo iterativno testiranje brez ročnega intervencije.Služijo kot zaščita pred neuspehi, ki bi se lahko zgodili po uvajanju, kar zagotavlja robustnost in zanesljivost digitalnih sistemov.

Ključne sestavine testnega stena in njihove funkcije

Če želite bolje razumeti, kako delujejo testne steze, je pomembno raziskati komponente, zaradi katerih so učinkovite.Dobro izdelan testnik deluje z upravljanjem dveh temeljnih nalog: ustvarjanje vhodov (dražljajev) in preverjanjem izhodov.Podrobno preučimo vsako komponento.

Generacija dražljajev

Generacija dražljajev vključuje ustvarjanje nabora vhodnih signalov, ki simulirajo pogoje za testiranje vedenja digitalnega sistema.Ti vložki morajo biti tako natančni kot realni, da se zagotovi, da je sistem podvržen različnim scenarijem, s katerimi bi se lahko srečala v praksi.Kot primer razmislite o osnovnem RAM modulu.Testbench mora v modul dobaviti posebne vhode in upoštevati njegove rezultate, da se zagotovi, kot je bilo pričakovano.Ključni vhodi za modul RAM običajno vključujejo:

• CLK (ura): poganja čas sistema.

• ADDR (naslov): Določi, katera lokacija podatkov za dostop do.

• wen (pisanje omogoči): nadzoruje, ali so podatki zapisani v pomnilnik.

• Podatki: dejanske informacije, zapisane v modul.

Izhod, znan kot DataOut, predstavlja rezultat notranjega operacij modula.S skrbnim scenarom, kako se ti vhodi dostavljajo, in spremljate Dataout, lahko preverite, ali sistem deluje pravilno v različnih scenarijih.Pomislite na ustvarjanje dražljajev kot postavitev testnega scenarija v laboratoriju.Tako kot znanstveniki skrbno nadzorujejo pogoje za opazovanje kemijskih reakcij, tudi digitalni oblikovalci izdelujejo natančne vhode, da opazujejo, kako se sistem odziva.

Preverjanje izhoda

Preverjanje izhoda je postopek preverjanja, ali dejanski izhodi sistema ustrezajo pričakovanim rezultatom.Ta korak je ključnega pomena pri lovljenju napak zgodaj, preden se razvijejo v večja vprašanja.Drugi uporabljajo preverjanje izhoda za potrditev, da sistem izpolnjuje predvideno funkcionalnost in deluje dosledno pod različnimi pogoji.Preverjanje izhoda vključuje avtomatizirane in ročne preverjanja.Na primer:

• Orodja za samodejno preverjanje: Orodja, kot sta ModelsIM in Quartus, omogočajo samodejno testiranje, kjer se sistemski izhodi primerjajo s pričakovanimi rezultati.To pospeši postopek preverjanja in zmanjšuje napako.

• Ročno preverjanje (neobvezno): Za bolj zapletene scenarije bodo morda potrebni ročni pregledi, da se zagotovi zajeta posebni ročni primeri.

Orodja in tehnike za izvajanje Testbench

Quartus: vizualna vhodna/izhodna simulacija

Quartus ponuja grafični vmesnik, ki vizualno razporedi vhode in opazuje izhode.Ta metoda je lahko koristna za začetnike ali za sisteme, ki zahtevajo bolj praktični, vizualni pristop.Če dovoli interakcijo s simulacijo skozi grafično okolje, Quartus pomaga demistificirati razmerje med vhodi in izhodi, kar olajša razumevanje, kako se digitalni sistem obnaša pravočasno.Ena ključnih prednosti Quartusa je, da je idealen za začetnike.Njegov intuitiven, vizualni vmesnik omogoča preprost način, kako vhodi vplivajo na izhode, ne da bi potrebovali obsežno skriptno ali programiranje znanja.Povratne informacije, ki jih ponuja, pomagajo lažje dojemati vedenje vezij, s čimer je koristno orodje za tiste nove za digitalno oblikovanje sistema.Vendar ima Quartus svoje omejitve.Nastavitev simulacij v Quartusu je lahko zamudna, zlasti za bolj zapletene zasnove.Orodje je manj prilagodljivo v primerjavi s simulacijskimi orodji, ki temeljijo na scenarijih, ki lahko ponujajo več možnosti prilagajanja in avtomatizacije.Za delo na obsežnih ali zelo podrobnih sistemih lahko to pomanjkanje prilagodljivosti predstavlja izziv.

ModelSim: besedilna simulacija z uporabo skript

ModelSim uporablja drugačen pristop k simulaciji z prednostno nalogo besedila, ki temelji na besedilu s scenarijem.Ustvarite testne scenarije z uporabo skriptov Verilog (.V) ali VHDL (.vhd), namesto da vizualno uredite vhode in izhode.Ta metoda zagotavlja več natančnosti in nadzora.Namesto da se zanašate na grafični vmesnik, določite, kako je treba sistem preizkusiti s podrobnimi skripti, kar omogoča večjo prilagoditev in avtomatizacijo v procesu simulacije.Ena izmed ključnih prednosti ModelSiM je prilagodljivost, ki jo ponuja.Z uporabo skript imate več nadzora nad scenariji testiranja, kar jim omogoča, da ustvarijo zapletene in natančne simulacije.Ko oblikovalec pozna sintakso in delovni tok, je nastavitev simulacij lahko veliko hitrejša v primerjavi z uporabo grafičnih orodij, kot je Quartus.Sposobnost ponovne uporabe in spreminjanja skript dodaja tudi njegovo učinkovitost, zlasti pri večjih projektih.Vendar pa besedilni pristop modelSIM prihaja z določenimi omejitvami.Zahteva trdno razumevanje sintakse Verilog ali VHDL, ki lahko predstavlja izziv za začetnike, ki niso seznanjeni z jeziki opisa strojne opreme.Kot rezultat, ima ModelSIM bolj strmo krivuljo učenja v primerjavi z več vizualnimi simulacijskimi orodji.Novi uporabniki morda težko začnejo, toda s prakso lahko natančnost in prilagodljivost, ki jo ponuja skripta, postaneta dragocena prednost.

Teorija premostitve in praksa pri preverjanju

Testnike služijo kot most med teoretičnimi dizajni in aplikacijami, tako da simulirajo, kako se bo digitalni sistem obnašal pod različnimi pogoji, vključno z robnimi primeri in nepričakovanimi vhodi.V digitalnem oblikovanju je pogosto težko napovedati, kako bo sistem v praksi deloval izključno na teoretičnih modelih.Testbente zaprejo to vrzel, tako da omogočajo, da presežete abstraktne koncepte oblikovanja in ocenite vedenje sistema v nadzorovanem, simuliranem okolju.Ena ključnih prednosti uporabe simulacijskih orodij v testnih stenah so takojšnje povratne informacije, ki jih zagotavljajo med odpravljanjem napak.Orodja, kot sta MultiSIM ali ModelSIM, ponujajo vizualne predstavitve sistema, ki prikazuje, kako spremembe vhodov vplivajo na izhode sčasoma.Ta povratna informacija vam omogoča, da hitreje natančno določite težave, sledite napakam nazaj do njihovega koreninskega vzroka in ustrezno prilagodite njihove zasnove.Na primer, če sistem ne izpolnjuje časovnih omejitev ali ima nepričakovano vedenje pod določenimi vhodnimi sekvencami, lahko tesnik takoj poudari te pomanjkljivosti, dolgo, preden je sistem fizično zgrajen.Z zgodnjim prepoznavanjem vprašanj v ciklu načrtovanja testnike zmanjšujejo potrebo po dragi predelavi in fizičnem prototipiranju, kar racionalizira postopek preverjanja.Ta zgodnja validacija pomaga zagotoviti, da so digitalni sistemi funkcionalno pravilni in prožni na pogoje, zaradi česar so bolj zanesljivi in zmanjšajo tveganje za neuspeh po uvajanju.Na ta način Testbenches delujejo kot praktično orodje za preoblikovanje teoretičnih modelov v robustne.

Napredna arhitektura Testbench

Napredni testni preskusi presegajo preprosto testiranje vhoda-izhod z vključitvijo dodatnih komponent za upravljanje zapletenih sistemov.Standardni test vključuje tri ključne dele: a Stimulus Generator Za ustvarjanje vhodnih signalov, a Oblikovanje v testu (DUT), kar je dejanska strojna oprema, ki se preizkuša, in Izhodni monitor To preverja rezultate glede na pričakovane rezultate.Te komponente sodelujejo pri zagotavljanju natančnejšega in natančnega preverjanja digitalnih modelov.

Izboljšanje natančnosti testnega koraka vključuje uporabo tehnik, ki zagotavljajo, da oblikovanje zanesljivo deluje v različnih scenarijih. Randomizirano testiranje Uvaja nepredvidljive vhodne vzorce za preverjanje stabilnosti sistema pod različnimi pogoji. Testiranje primerov Osredotoča se na mejne situacije, ko sistem najverjetneje naleti na napake.Nazadnje, Regresijsko testiranje Vključuje ponovne teste po spremembah, da se potrdi, da ni bila uvedena nova vprašanja, saj zagotavlja, da sistem ostane dosleden in brez napak sčasoma.

Skriptne testne mine

Če želite ustvariti učinkovite in zanesljive testne steze v Verilogu ali VHDL, sledite ključnim najboljšim praksam.Začnite preprosto, nato razširite tako, da najprej preizkusite osnovno funkcionalnost in postopoma dodajate bolj zapletene scenarije.Uporabite komentarje in dokumentacijo, da olajšate in vzdržujete svoje skripte z jasno razlago vsakega razdelka.Nazadnje avtomatizirate, kadar je to mogoče, da prihranite čas in zmanjšate napake z uporabo zank in funkcij za ravnanje s ponavljajočimi se nalogami in vhodnimi vzorci.

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Digitalna zanka s fazo (DPLL): Oblikovanje, komponente in operacije

na 2025/01/7

Evolucija in vpliv arhitekture RISC v sodobnem računalništvu

na 2025/01/7

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/18 147778

-

USB-C pinout in funkcije

na 2000/04/18 112033

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/18 111352

-

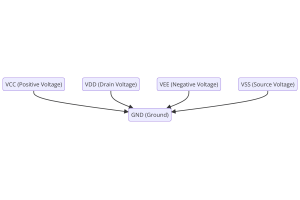

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/18 83792

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79596

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66976

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63110

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63043

-

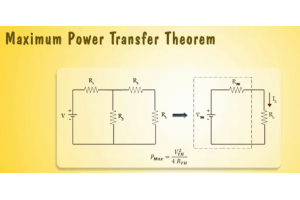

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54097

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52197