EP1C4F400C8 FPGA: Funkcije, specifikacije, programiranje in alternative

Če delate s programirljivo logiko, vam EP1C4F400C8 omogoča praktično ravnovesje zmogljivosti in stroškov.V tem članku boste izvedeli, kaj je ta FPGA, njegove ključne lastnosti, kot so logična zmogljivost, pomnilnik in možnosti V/I, in kako njegova struktura podpira zanesljiv dizajn.Opazili boste tudi njegove specifikacije, aplikacije v sistemih, proces programiranja in kako se primerja s podobnimi deli.Katalog

Kaj je EP1C4F400C8?

The EP1C4F400C8 je član Intelove (prej Altera's) Cyclone FpGA družine, zasnovane kot stroškovno učinkovita in zanesljiva programirljiva logična rešitev.Ta naprava, zgrajena v postopku 0,13 µm SRAM, ponuja zmerno logično gostoto in prilagodljive možnosti V/I v kompaktnem paketu FBGA-400.Družina ciklona, ki vključuje naprave, kot so EP1C3, EP1C6, EP1C12 in EP1C20, je bila ustvarjena za uravnoteženje zmogljivosti in cenovne dostopnosti za razširljive modele, kar omogoča enostavno migracijo med stopnjami gostote in paketi.Znana po stabilnosti in širokem sprejetju, ostaja zaupanja vreden izbira v zapuščenih modelih.

Iščete EP1C4F400C8?Pišite nam, da preverite trenutne zaloge, čas svinca in cene.

EP1C4F400C8 CAD modeli

Simbol EP1C4F400C8

EP1C4F400C8 FISPInt

EP1C4F400C8 3D model

Funkcije EP1C4F400C8

• Logična zmogljivost

EP1C4F400C8 ponuja približno 4000 logičnih elementov, organiziranih v 400 logičnih blokov (laboratorij).Zaradi tega je primeren za modele srednjega dosega, ki zahtevajo zmerno logično gostoto, hkrati pa ohranjajo stroškovno učinkovitost.

• Vgrajen pomnilnik

Vključuje približno 76,5 kbitov vgrajenega pomnilnika.Ta notranji RAM podpira funkcije za pufer, shranjevanje in majhne pomnilnike, kar zmanjšuje potrebo po zunanjih komponentah pomnilnika v mnogih modelih.

• Visoko število V/I.

Naprava ponuja 301 uporabniških zatičev, ki jih je mogoče konfigurirati v svojem paketu FBGA s 400 kroglicami.To visoko število PIN -a omogoča bogato povezljivost za zapletene sisteme, ki zahtevajo več perifernih vmesnikov.

• Široka podpora za standarde I/O

Podpira več standardov V/I, vključno z LVTTL, LVCMOS, SSTL-2, SSTL-3 in diferencialnimi LVD-ji.Ta prilagodljivost omogoča, da se FPGA neposredno poveže z različnimi sodobnimi logičnimi družinami in pomnilniškimi napravami.

• Hitro diferencialna signalizacija

S podporo LVD -jev do 640 Mbps, FPGA obravnava zahteve za hitro prenos podatkov.Zaradi tega je praktično za aplikacije, kot so komunikacijske povezave za visoke hitrosti in hitri digitalni vmesniki.

• Upravljanje ur s PLLS

Čip združuje dve fazni zanki (PLL) in osem globalnih omrežij.Te funkcije omogočajo natančno ustvarjanje ur, množenje in nadzor tresenja za časovno kritične aplikacije.

• Delovanje jedra z nizko napetostjo

Naprava, ki deluje pri nazivni 1,5 V jedrni napetosti, uravnoteži zmogljivost z nižjo porabo energije.Ta napetostna raven je bila optimizirana za 0,13 µm CMOS tehnologijo, ki se uporablja pri izdelavi.

• Prilagodljive V/I napetosti

FPGA podpira V/I napetosti 1,5 V, 1,8 V, 2,5 V in 3,3 V v različnih bankah.Ta vsestranskost mu omogoča, da se poveže tako z zapuščenimi kot sodobnimi sistemskimi komponentami.

• Konfiguracija na osnovi SRAM

Tako kot drugi ciklonski FPGA je tudi na osnovi SRAM in zahteva rekonfiguracijo pri vsakem vklopu.To zagotavlja prilagodljivost za posodobitve, zahteva pa tudi zunanjo konfiguracijsko napravo ali krmilnik.

• Podpora za stiskanje bitstream

EP1C4F400C8 med konfiguracijo podpira stisnjeno bitstream nalaganje.To zmanjšuje zahteve po zunanjem pomnilniku in pospeši čas konfiguracije.

• Skladnost s PCI

Vključuje vgrajeno podporo za standarde PCI (33/66 MHz, 32/64-bit).Ta funkcija omogoča, da se naprava neposredno vključi v sisteme, ki zahtevajo povezovanje PCI brez dodatne premostitvene logike.

Laboratorijska struktura ciklona

Diagram prikazuje strukturo logičnega matričnega bloka (LAB), ki se uporablja v ciklonskih FPGA, kot je EP1C4F400C8.Vsak laboratorij se poveže z omrežjem medsebojnih povezav: medsebojno povezovanje vrstic, medsebojno povezovanje stolpcev in lokalne medsebojne povezave, ki signalizirajo poti med logičnimi elementi in drugimi bloki.Medsebojne povezave z neposrednimi povezavami zagotavljajo hitre poti, nizke zamude do sosednjih laboratorijev, kar izboljšuje časovno delovanje v signalnih poteh.Ta arhitektura je pomembna, ker uravnoteži prilagodljivost prilagodljivosti z učinkovitostjo, kar omogoča FPGA, da obvlada zapletene zasnove, hkrati pa ohranja hitrost in optimizirano območje.

Diagram bank ciklona V/I

Diagram prikazuje V/I bančno strukturo ciklonskih FPGA, kot je EP1C4F400C8.Naprava je razdeljena na štiri V/I banke, ki jih poganja lastni dovodni vodilo, kar omogoča mešanje različnih napetostnih standardov v enem samem FPGA.Vse banke podpirajo široko paleto V/I standardov, vključno z LVTTL, LVCMO, LVDS, RSD in SSTL, medtem ko banke 1 in 3 podpirajo tudi 3,3-V PCI za združljivost s zapuščenimi sistemi.Ta prilagodljiva V/I arhitektura je pomembna, saj omogoča brezhibno integracijo z raznolikimi zunanjimi napravami in vmesniki, zaradi česar je FPGA prilagojena različnim aplikacijam.

Specifikacije EP1C4F400C8

|

Tip |

Parameter |

|

Proizvajalec |

Altera/Intel |

|

Serija |

Cyclone® |

|

Embalaža |

Pladenj |

|

Status dela |

Zastarelo |

|

Število laboratorijev/CLB |

400 |

|

Število logičnih elementov/celic |

4000 |

|

Skupni ovnovski koščki |

78,336 |

|

Število V/I. |

301 |

|

Napetost - dovod |

1.425V ~ 1.575V |

|

Vrsta pritrditve |

Površinski nosilec |

|

Delovna temperatura |

0 ° C ~ 85 ° C (TJ) |

|

Paket / ohišje |

400-BGA |

|

Paket dobaviteljskih naprav |

400-FBGA (21 × 21) |

|

Številka osnovnega izdelka |

EP1C4 |

Aplikacije EP1C4F400C8

1. digitalna obdelava signalov (DSP)

EP1C4F400C8 je mogoče programirati za izvajanje nalog, kot so filtriranje, FFT in signalna modulacija.Njegova kombinacija logičnih elementov in vgrajenega pomnilnika je primerna za hitro obdelavo.To mu omogoča, da tradicionalne DSP čipe zamenja s prilagodljivo raztopino FPGA, ki jo je mogoče reprogramirati za različne algoritme.

2. vdelani in krmilni sistemi

V industrijskih in vgrajenih sistemih se ta FPGA pogosto uporablja za izvajanje krmilnikov, sekvenčnikov in državnih strojev po meri.Njegova rekonfiguracijska logika omogoča prilagajanje strojne opreme natančno na potrebe sistema.Z vključitvijo krmilne logike znotraj FPGA se število zunanjih komponent zmanjša, kar izboljša zanesljivost in zniža stroške.

3. Komunikacija in premostitev vmesnika

Naprava podpira več V/I standardov in lahko deluje kot most med različnimi komunikacijskimi protokoli.Pogosto se uporablja za povezavo PCI, LVD -jev, SDRAM in drugih vmesnikov v sistemu.Zaradi tega je zelo koristno pri omrežni opremi, vgrajenih krmilnikih in pretvorbi vmesnikov zapuščine.

4. Pridobitev in obdelava podatkov

EP1C4F400C8 je z visoko razpoložljivostjo I/O in prilagodljiv pomnilnik dobro primeren za sisteme zbiranja podatkov.Lahko se neposredno poveže z ADC -ji in senzorji, podatke obdela pravočasno in jih pripravi na shranjevanje ali prenos.Takšne aplikacije so pogoste v medicinskih instrumentih, preskusni opremi in znanstvenih merilnih napravah.

EP1C4F400C8 Podobni deli

|

Specifikacija |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Proizvajalec |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

Družina FPGA |

Ciklon (EP1C4) |

Ciklon (EP1C4) |

Ciklon (EP1C4) |

Ciklon (EP1C4) |

Ciklon (EP1C4) |

Ciklon (EP1C4) |

|

Logični elementi (LES) |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

|

Vgrajen pomnilnik (biti) |

~ 76,5 Kbit |

~ 76,5 Kbit |

~ 76,5 Kbit |

~ 76,5 Kbit |

~ 76,5 Kbit |

~ 76,5 Kbit |

|

I/o zatiči |

301 |

301 |

301 |

301 |

249 |

97 |

|

Paket / ohišje |

400-FBGA |

400-FBGA |

400-FBGA |

400-FBGA |

324-FBGA |

144-TQFP |

|

Hitrost |

C8 |

C8 |

C8 |

C6 (hitreje) |

C8 |

C8 |

|

Jedrna napetost |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

|

Delovna temperatura.Domet |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C.

|

Koraki programiranja EP1C4F400C8

Preden lahko uporabite EP1C4F400C8 FPGA, morate svoj dizajn naložiti v napravo.Programiranje vključuje konfiguriranje FPGA z bitstream datoteko, tako da se zna obnašati kot vaše predvideno vezje.

1. izberite shemo konfiguracije in nastavite MSEL

Začnete z izbiro sheme konfiguracije, ki najbolje ustreza vaši nastavitvi, kot so aktivna serijska, pasivna serijska ali JTAG.To se naredi tako, da pred vklopom nastavite zatiče MSEL na določene logične ravni.Vsak način uporablja različne zatiče in protokole, zato morate potrditi združljivost s svojimi oblikovalskimi orodji in konfiguracijskim pomnilnikom.Prava izbira tukaj zagotavlja nemoten postopek konfiguracije.

2. Uporabite napajanje in inicializirajte napravo

Nato vklopite jedro FPGA in V/I tirnice v določenem območju napetosti.Med zagonom naj bo Nconfig Pin nizka, da napravo držite v ponastavitvi, dokler napačne napetosti niso stabilne.Ko stabilni, sprostite ponastavitev in napravo signalizirajo pripravljenost z vožnjo NSTATUS PIN.To zagotavlja, da se FPGA pravilno inicializira, preden se začne konfiguracija.

3. Prenos konfiguracije bitstream

Na tej stopnji pošljete konfiguracijsko datoteko (Bitstream) v FPGA s pomočjo izbrane sheme.V aktivnem serijskem ali pasivnem serijskem načinu bitstream prihaja iz zunanje pomnilniške naprave, JTAG pa omogoča neposredno programiranje prek kabla.Naprava nenehno bere v konfiguracijskih podatkih, dokler ni končana.Vaša oblikovalska programska oprema ustvarja to bitstream, da ustreza vašim logičnim zahtevam.

4. Potrdite uspešno konfiguracijo (konf_done)

Ko FPGA zaključi nalaganje, uveljavlja pin Conf_done, da pokaže, da so bili konfiguracijski podatki uspešno sprejeti.Hkrati naprava izvaja notranjo inicializacijo, kot so čiščenje registrov in aktiviranje V/I.Če Conf_done ne gre visoko, to običajno pomeni, da imajo konfiguracijski podatki ali nastavitev napako.Gledanje tega zatiča je najpreprostejši način za preverjanje postopka.

5. Izvedite neobvezno konfiguracijo v sistemu

Končno imate možnost posodobiti ali reprogramirati FPGA, ne da bi ga odstranili s plošče.Z JTAG ali vgrajenim krmilnikom lahko neposredno naložite nov bitstream, kar je uporabno za posodobitve vdelane programske opreme.Ta prilagodljivost vam omogoča spreminjanje, odpravljanje napak ali nadgradnjo sistema tudi po uvajanju.Zagotavlja, da se lahko vaš dizajn, ki temelji na FPGA, sčasoma prilagodi spreminjajočim se zahtevam.

EP1C4F400C8 Prednosti in slabosti

Prednosti

• stroškovno učinkovita izbira za modele srednjega dosega

• Visoko število V/I v primerjavi s podobnimi napravami za gostoto

• Prilagodljiva napetost in standardna podpora V/I

• Podprto z zrelimi orodji in dokumentacijo

• Nižja poraba energije kot starejše generacije FPGA

Slabosti

• zastarel z omejeno dolgoročno razpoložljivostjo

• Nižja logika in zmogljivost pomnilnika v primerjavi s sodobnimi FPGA

• Počasnejša hitrost obratovanja in zmogljivost V/I

• Za konfiguracijo pri vklopu zahteva zunanji pomnilnik

• Manjka napredne funkcije, kot so bloki DSP in hitri oddajniki

EP1C4F400C8 Dimenzije embalaže

|

Tip |

Parameter |

|

Vrsta paketa |

FBGA (matrika krogličnega omrežja z drobnim točkam) |

|

Število kroglic |

400 |

|

Žoga (e) |

1,0 mm (značilno za ciklon EP1C4F400) |

|

Premer kroglice (b) |

0,45 mm (nominalno) |

|

Velikost paketa (d × e) |

21 mm × 21 mm |

|

Višina paketa (a) |

2,40 mm (max) |

|

Debelina substrata (A2) |

~ 0,40 mm |

|

Debelina kalupa (A3) |

~ 1,90 mm |

|

Višina kroglice (A1) |

0,25 mm (nazivno) |

|

Pin A1 kotiček |

Označena za orientacijo |

|

Postavitev niza |

Grid 20 × 20 (manjkajo z vogalnimi kroglicami) |

|

Pritrditev |

Površinski nosilec (SMD) |

EP1C4F400C8 Proizvajalec

EP1C4F400C8 je prvotno izdelal Altera Corporation, pionir v programirljivih logičnih napravah in tehnologiji FPGA.Leta 2015 je Altera pridobila Intel Corporation, in linija izdelkov je postala del Intelove programirljive rešitve skupine (PSG).Danes Intel podpira te zapuščene naprave Altera, hkrati pa se osredotoča na novejše družine FPGA, kar zagotavlja kontinuiteto za obstoječe uporabnike in napreduje inovacije v programirljivi logiki.

Zaključek

EP1C4F400C8 izstopa kot stroškovno učinkovit in vsestranski FPGA, ki ponuja trdne zmogljivosti za modele srednjega razreda.S svojimi 4000 logičnimi elementi, vgrajenim pomnilnikom, obsežno podporo V/I in združljivostjo z več napetostnimi in vmesniškimi standardi zagotavlja prilagodljivost med različnimi aplikacijami.Njegova arhitektura, proces programiranja in široka uporabnost v DSP, vgrajenih sistemih in pridobivanju podatkov omogočajo praktično izbiro kljub zapuščine.Medtem ko nima naprednih funkcij, ki jih najdemo v novejših napravah in se sooča z omejeno dolgoročno razpoložljivostjo, ostaja zanesljiva možnost, ki išče dokazane rešitve v razširljivih FPGA modelih.

PDF podatkovnega lista

EP1C4F400C8 podatkovne liste:

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Pogosto zastavljena vprašanja [FAQ]

1. Katera orodja so potrebna za programiranje EP1C4F400C8?

Potrebujete Intelovo Quartusovo programsko opremo (prej Altera Quartus II), skupaj s podprtim programskim kablom, kot je USB-Blaster.Ta orodja vam omogočajo, da ustvarite bitstream in ga naložite v FPGA.

2. Ali lahko neposredno EP1C4F400C8 roči PCI aplikacije?

Da, ima vgrajeno skladnost za standarde PCI (33/66 MHz, 32/64-bit), zaradi česar je primeren za sistemsko integracijo, ki temelji na PCI, ne da bi potrebovali dodatno logiko premostitve.

3. Kaj se zgodi, če EP1C4F400C8 med konfiguracijo ne uspe?

Če konfiguracija ne uspe, Pin Conf_done ne bo trdil visoko.To ponavadi kaže na napako v datoteki bitstream, sekvenciranju napetosti ali nastavitvi zatiča in ga je treba ponovno preveriti v vašem oblikovalskem toku.

4. Ali lahko vmesnik EP1C4F400C8 neposredno s pomnilnikom DDR?

Podpira več standardov V/I, vendar nima domačih vmesnikov DDR, kot so sodobni FPGA.Morda bodo potrebni dodatni oblikovni vidiki ali premostitvene komponente.

5. Kako se EP1C4F400C8 primerja z novejšimi FPGA?

V primerjavi s sodobnimi napravami ima EP1C4F400C8 nižjo hitrost, manj logične gostote in manj naprednih funkcij.Vendar ostaja stroškovno učinkovita izbira za stabilne modele srednjega dosega, kjer ni potrebna vrhunska zmogljivost.

Pregled EPM3256AFC256-7 CPLD: Funkcije, pinout, programiranje in aplikacije

na 2025/10/3

ADG432BR Analogno stikalo IC: Specifikacije, pinout, alternative in podatkovni list

na 2025/10/2

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/18 147776

-

USB-C pinout in funkcije

na 2000/04/18 112022

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/18 111351

-

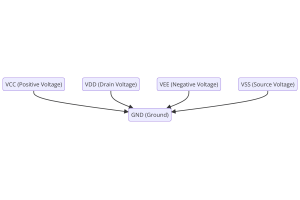

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/18 83777

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79575

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66964

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63104

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63041

-

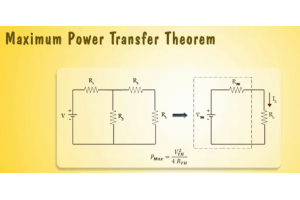

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54097

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52189