EPF6016ATC144-2N FPGA: Funkcije, programiranje, aplikacije in alternative

Ta vodnik govori o EPF6016ATC144-2N, vrste čipa, imenovanega FPGA.Uporablja se v digitalnih sistemih, ki morajo biti prilagodljivi in enostavni za posodobitev.Vodnik pojasnjuje, kaj počne čip, kako deluje, njene glavne dele in lastnosti, kako ga uporabiti in programirati, kje ga je mogoče uporabiti in zakaj je še danes dobra izbira.Katalog

Kaj je EPF6016ATC144-2N?

The EPF6016ATC144-2N je član družine Flex 6000 FPGA, ki jo je razvila Altera, ki je zdaj del Intela.Ta naprava je bila zgrajena na reprogramirani logiki, ki temelji na SRAM, zasnovana za prilagodljivost v digitalnih logičnih aplikacijah srednje gostote.Uporablja arhitekturo Optiflex, ki združuje logične matrične bloke (laboratoriji) in visoko hitrost medsebojne povezave za zagotavljanje učinkovite uporabe virov in hitrega usmerjanja signala.EPF6016ATC144-2N podpira rekonfiguracijo v sistemu, zaradi česar je idealen za modele, ki zahtevajo posodobitve ali spremembe po uporabi.Kot del serije Flex 6000 ponuja stroškovno učinkovito rešitev za zamenjavo tradicionalnih matrikov vrat, hkrati pa poenostavi razvojni cikel.

Iščete EPF6016ATC144-2N?Pišite nam, da preverite trenutne zaloge, čas svinca in cene.

EPF6016ATC144-2N CAD modeli

Simbol EPF6016ATC144-2N

EPF6016ATC144-2N FISPInt

EPF6016ATC144-2N 3D model

Funkcije EPF6016ATC144-2N

• Logična zmogljivost

EPF6016ATC144-2N ponuja približno 16.000 sistemskih vrat, ki se izvajajo z uporabo 1.320 logičnih elementov (LES) v 132 logičnih blokih (laboratoriji).To zagotavlja zmerno zapletenost, primerno za aplikacije FPGA srednjega dosega.

• I/o zatiči

Podpira do 117 uporabniških zatičev, ki jih je mogoče konfigurirati.Ti zatiči omogočajo prožno povezavo z različnimi sistemskimi komponentami in zunanjimi napravami.

• Jedrna napetost

Jedro deluje pri 3.3V s funkcionalnim območjem od 3,0V do 3,6 V. To omogoča združljivost s standardnimi digitalnimi sistemi z nizko napetostjo.

• V/I napetost

Njegova multivoltna V/I funkcija podpira povezovanje z napravami z nivojem 3.3V ali 2,5V.To poenostavi integracijo v okolje z mešano napetostjo.

• Delovna temperatura

Standardno temperaturno območje delovnega stika je od 0 ° C do +85 ° C.To podpira tipično komercialno in industrijsko okolje.

• Dovodni tok

Med normalnim delovanjem nariše približno 5mA in v stanju pripravljenosti manj kot 0,5 mA.To pomaga ohranjati moč v energetsko ozaveščenih modelih.

• Hitrost ure (hitrost –2n)

S hitrostjo –2 dosega notranje logične frekvence do približno 166MHz.To omogoča hitro izračun pri obdelavi signalov ali logiki nadzora.

• Arhitektura

Na podlagi Altera's Optiflex Architecture uporablja logiko, ki temelji na LUT, z namenskimi usmerjevalnimi viri.Ta arhitektura ponuja visoko logično gostoto in učinkovito delovanje.

• Hitri medkonnect

Usmerjevalna mreža Fasttrack omogoča signalne poti z nizko zakasnitvijo in podpira prenos podatkov z visokimi hitrostmi v logičnih blokih.To prispeva k doslednemu času in uspešnosti.

• Vzpostavljena konfiguracija v vezju

Uporablja logično konfiguracijo na osnovi SRAM, kar omogoča, da se FPGA reprogramira v sistemu.To podpira posodobitve oblikovanja ali dinamično prilagoditev strojne opreme brez odstranitve.

• JTAG mejno skeniranje

Naprava vključuje IEEE 1149.1-skladno logiko JTAG meje.To olajša odpravljanje napak in vsistemsko preverjanje odborov in medsebojnih povezav.

• Podpora za vroče sekete

Lahko ga varno vstavite ali odstranite med napajanjem v sistemih 3.3V.Ta funkcija je uporabna na modularnih ali uporabnih strojnih platformah.

• Funkcionalno testiranje

Vsaka enota je v celoti funkcionalno preizkušena pred odpremo.To zagotavlja kakovost in odpravlja potrebo po uporabniško določenih testnih vektorjih med razvojem.

• Združljivost PCI

Naprava je združljiva s PCI Local Bus Revision 2.2 za 5V delovanje.To omogoča, da se uporablja v zapuščenih vgrajenih sistemih, ki temeljijo na PCI.

Diagram bloka arhitektur Optiflex

Diagram prikazuje, kako so organizirani in povezani notranji deli FPGA.V središču so bloki logične matrike (laboratoriji), to so glavne gradbene enote čipa.Vsak laboratorij vsebuje več logičnih elementov (LES), ki izvajajo osnovne digitalne operacije, kot so logična vrata in flip-flops.Laboratoriji so povezani z lokalnim povezovanjem, ki omogoča učinkovito sodeluje logika znotraj vsakega bloka.Za širšo komunikacijo po čipu se laboratoriji povezujejo do vrst in stolpcev Fasttrack medsebojno povezovanje, hitre signalne poti, ki omogočajo, da se podatki hitro premikajo iz enega dela čipa na drugega z majhno zamudo.Okoli zunanjih robov diagrama so vhodni/izhodni elementi (IOE).Ti povezujejo notranjo logiko FPGA z zunanjimi napravami s pretvorbo med logiko čipa in napetostnimi nivoji, ki jih uporabljajo druga strojna oprema.Ta postavitev s svojimi modularnimi bloki in hitrimi potmi usmerjanja odraža prilagodljivost in osredotočenost zmogljivosti arhitekture Optiflex.

Flex 6000 Model časovni model

Časovni model Flex 6000 prikazuje, kako se signali premikajo in se zamujajo, ko potujejo skozi FPGA.V središču modela so logični elementi (LES), ki obdelujejo podatke in kontrolne signale s posebnim časom.Vsak LE se poveže s časovnimi potmi, kot sta T_DATA_TO_REG in T_REG_TO_OUT, ki določajo, koliko časa traja, da signali vstopijo, obdelajo in zapustijo logiko.

Zraven Les so posebne poti, imenovane laboratorijske in laboratorijske kaskade.Ti signali omogočajo, da se premikajo vodoravno med logičnimi elementi v istem bloku in podpirajo hitre operacije, kot so dodatki in primerjave.Te poti imajo tudi svoje časovne vrednosti, kot sta T_CARRY_TO_REG in T_CASC_TO_OUT, za merjenje zamud med temi operacijami.

Na dnu diagrama vhodni/izhodni elementi (IOE) prenašajo signale, ki gredo v in iz čipa.Vključujejo točke zamude, kot je T_IN_DELAY, ki upoštevajo različice pri prejemanju podatkov iz zunanjih naprav.

Model vključuje tudi usmerjevalne poti na različnih ravneh (t_local, t_row, t_col in t_global), ki predstavljajo, kako daleč potuje signal in koliko časa traja.Te poti pomagajo razumeti in obvladovati zamude v različnih delih čipa, kar olajša doseganje uspešnosti in časovnih ciljev.

Specifikacije EPF6016ATC144-2N

|

Tip |

Parameter |

|

Proizvajalec |

Altera/Intel |

|

Serija |

Flex 6000 |

|

Embalaža |

Pladenj |

|

Status dela |

Zastarelo |

|

Število laboratorijev/CLB |

132 |

|

Število logičnih elementov/celic |

1320 |

|

Število V/I. |

117 |

|

Število vrat |

16000 |

|

Napetost - Dobava |

3V ~ 3,6V |

|

Vrsta pritrditve |

Površinski nosilec |

|

Delovna temperatura |

0 ° C ~ 85 ° C (TJ) |

|

Paket / ohišje |

144-LQFP |

|

Paket dobaviteljskih naprav |

144-TQFP (20x20) |

|

Številka osnovnega izdelka |

EPF6016 |

Aplikacije EPF6016ATC144-2N

1. Naloge digitalne obdelave signalov (DSP)

EPF6016ATC144-2N s 1.320 logičnimi elementi in hitrim povezovanjem podpira izvajanje majhnih do srednjega digitalnega obdelave signalov.Uporablja se lahko za ustvarjanje FIR filtrov po meri, jedra FFT ali vzporedno aritmetično logiko za transformacijo signala.Čeprav nimajo namenskih blokov DSP ali vgrajenih množilnikov, lahko njegova logika splošne namene obravnava ponavljajoče se več-akumulacijske operacije, primerne za vgrajeno zvočno obdelavo, filtriranje podatkov senzorjev in oblikovanje valov v kontrolnih ali komunikacijskih sistemih.

2. Vgrajena kontrolna in industrijska avtomatizacija

Naprava je primerna za vgrajene kontrolne aplikacije v industrijskih okoljih.Njegova sposobnost vmešavanja z mešano napetostjo V/I (2,5 V in 3,3 V), njegovo stabilno delovanje pod standardnimi komercialnimi temperaturami (0–85 ° C) in podporo za vročega razpoka so zanesljivi za integracijo v programirljive logične krmilnike (PLC), motorično krmilnimi enotami, instrumentacijskimi vmesniki in splošno avtomatizacijo.Rekonfigurabilnost omogoča dolgoročno prilagodljivost izdelka, kjer se lahko logika posodobi brez zamenjave strojne opreme.

3. Premostitev in logika vmesnika komunikacijskega protokola

Zahvaljujoč multivolt I/O podpore in učinkovitemu usmerjevalnemu omrežju lahko EPF6016ATC144-2N uporabite za izvajanje komunikacijskih vmesnikov po meri in protokol.Lahko zgradi UART, krmilnike SPI ali vzporedne prevajalce avtobusa, da omogoči interakcijo med neusklajenimi digitalnimi sistemi.Njegovo zmerno število V/I (117 GPIO) in notranje upravljanje ure podpirata tudi časovno občutljivo signalizacijo, zaradi česar je primerna za omrežno opremo, zapuščeno emulacijo avtobusa ali kot logični element lepila v večjih podatkovnih komunikacijskih sistemih.

4. Test na ravni plošče, odpravljanje napak in potrjevanje

EPF6016ATC144-2N z vgrajeno JTAG mejno-skeniranjem (IEEE 1149.1) podpira napredno testiranje na ravni plošče, ne da bi potrebovali zunanje logične sonde ali vsiljivo diagnostiko.Preveri lahko V/I povezljivost, zazna odprta ali kratka vezja in med proizvodnjo ali vzdrževanjem na terenu izvaja preverjanje v sistemu.Ta funkcija je uporabna v zapletenih večplastnih PCB ali v sistemih, kjer je tradicionalni dostop do preskusnih točk omejen ali nepraktičen.

EPF6016ATC144-2N Podobni deli

|

Lastnosti |

EPF6016ATC100-1 |

EPF6016ATC100-3N |

EPF6016ATC144-3N |

|

Proizvajalec |

Altera |

Intel (Altera Legacy) |

Intel (Altera Legacy) |

|

Družina |

Flex 6000 |

Flex 6000 |

Flex 6000 |

|

Logični elementi (LES) |

1.320 |

1.320 |

1.320 |

|

Število vrat (približno) |

16.000 |

16.000 |

16.000 |

|

Paket |

100-pin TQFP |

100-pin TQFP |

144-pin TQFP |

|

Uporabniški V/I zatiči |

81 |

81 |

117 |

|

Hitrost |

-1 (standard) |

-3n (velika hitrost) |

-3n (velika hitrost) |

|

Največja frekvenca ure |

Nižje (običajno ~ 100 MHz) |

Višje (do ~ 166 MHz) |

Višje (do ~ 166 MHz) |

|

Vrsta konfiguracije |

Na osnovi SRAM |

Na osnovi SRAM |

Na osnovi SRAM |

|

Napajalna napetost |

3.3 V. |

3.3 V. |

3.3 V. |

|

Vroče seka |

DA |

DA |

DA |

|

JTAG/mejno skeniranje |

DA |

DA |

DA |

|

Prijave |

Osnovna logika, kompaktni dizajni |

Hitrejša logika nadzora, kompaktna |

Visokozmogljivi sistemi, več V/I |

|

Razpoložljivost |

Zastarelo |

Zastarelo |

Zastarelo |

Koraki programiranja EPF6016ATC144-2N

1. Izberite način konfiguracije

EPF6016ATC144-2N podpira konfiguracijo na osnovi SRAM, kar pomeni, da zahteva programiranje pri vsakem napajanju.Naprava omogoča več konfiguracijskih shem, najpogosteje pasivno serijsko (PS) in pasivno vzporedno asinhrono (PPA).Način konfiguracije je določen s tem, kako je priključen MSEL PIN.Na primer, ko je MSEL nizka, naprava pričakuje, da bodo podatki poslani serijsko prek zunanjega EEPROM (na primer EPC1) ali kabla za prenos.Izbira pravilne konfiguracijske metode je odvisna od zasnove sistema, na osnovi EEPROM za samodejni zagon ali kabel, ki temelji na prototipiranju in testiranju.

2. Sestavite zasnovo FPGA in ustvarite programsko datoteko

Če želite programirati FPGA, morate najprej ustvariti oblikovanje strojne opreme s pomočjo Intelovega Quartus ali Legacy Max+Plus II Design programske opreme.Po kompilaciji orodje ustvari SOF (SRAM objektna datoteka), ki predstavlja konfigurirano logiko.Ta SOF je treba nato pretvoriti v obliko, ki je združljiv z izbrano metodo konfiguracije:

• .rbf ali .POF za naprave EEPROM (npr. EPC1).

• .TTF ali .HEX za mikrokontroler ali vzporedno nalaganje.

Pretvorba se izvede z vgrajenim pripomočkom za pretvorbo datotek v programski opremi za oblikovanje.Ta korak zagotavlja, da je bitstream pravilno oblikovan za razlago FPGA.

3. Programirajte konfiguracijski pomnilnik (če uporabljate EEPROM)

V aplikacijah, kjer se uporablja serijska konfiguracijska naprava, kot je EPC1, je naslednji korak nalaganje konfiguracijskih podatkov v EEPROM.Običajno se to izvaja z orodjem za programiranje na namizju (npr. Programerja Max+Plus II ali Quartus).Postopek vključuje namestitev EEPROM v programsko vtičnico ali ga povezati v vezju, nalaganje ustrezne programske datoteke (običajno .POF ali .RBF) in začetek programskega cikla.Ko bo programiran, bo EEPROM samodejno zagotovil konfiguracijske podatke FPGA vsakič, ko sistem napade, kar bo odpravilo potrebo po ročnem reprogramiranju.

4. Konfigurirajte s kablom za prenos (pasivno serijsko)

Alternativa zagonu, ki temelji na EEPROM, je uporaba kabla za prenos (na primer USB-Blaster ali ByteBlaster) za neposredno konfiguriranje FPGA.Pri tej metodi povežete kabel z računalnikom in FPGA -jem NCONFIG, DCLK, DATA IN CONF_DONE.S programerjem Quartus sprožite postopek konfiguracije, ki ugasne Nconfig nizko, da se začne.Orodje nato konfiguracijske podatke serijsko pošlje po podatkovni vrstici, ki jo ureja DCLK.Postopek je končan, ko konf_done postane visoko, kar kaže na uspešno konfiguracijo in prehod naprave v uporabniški način.

5. Konfigurirajte z mikrokontrolerjem (pasivni serijski/vzporedni)

Če vaš sistem uporablja vgrajen mikrokontroler, lahko deluje tudi kot konfiguracijski glavni FPGA.V tej nastavitvi mikrokontroler trdi, da je Nconfig Low, da ponastavi FPGA, nato pa konfiguracijski bitstream premakne skozi podatke med preklopom DCLK.Zahteve za časovne razporeditve je treba spoštovati, čas nastavitve podatkov pred uro in čas zadrževanja sta dobra za uspešno konfiguracijo.Mikrokontroler lahko spremlja nožice NSTATUS in Conf_done, da zazna napake v konfiguraciji ali potrdi uspešno dokončanje.Ta metoda ponuja popoln nadzor nad konfiguracijskim postopkom in podpira dinamične posodobitve v polju.

6. Spremljajte konfiguracijske signale

Med postopkom konfiguracije FPGA zagotavlja povratne informacije prek statusnih zatičev:

• nStatus označuje zaznavanje napak;Če pride do napake (npr. Napaka CRC ali kršitev časovne kršitve), je nizka.

• Conf_done je visoko, ko se vsi konfiguracijski biti uspešno naložijo in preverijo.

Če NSTATUS ostane visok in se na koncu zaporedja prehodi Conf_done, naprava samodejno vstopi v uporabniški način, kjer uporabniško določena logika postane aktivna.To spremljanje signala je pomembno, da se postopek programiranja uspešno zaključi.

7. Po potrebi izvedite rekonfiguracijo

Ker je EPF6016ATC144-2N na osnovi SRAM, ga je mogoče kadar koli ponovno konfigurirati s preklopom Nconfig PIN-a, ki ponastavi napravo in znova zažene konfiguracijski cikel.Ta funkcija omogoča prilagodljive posodobitve sistema in spremembe med delovanjem brez fizične zamenjave.Sposobnost ponovne konfiguracije, medtem ko v krogu podpira tudi odvečnost, dinamično zamenjavo funkcij ali popravljanje napak po uvajanju.Zaradi tega je naprava zelo primerna za aplikacije, ki zahtevajo prilagodljivost ali dolgo življenjsko dobo.

8. Upoštevajte časovne in električne zahteve

Programiranje EPF6016ATC144-2N uspešno zahteva tudi pozornost na električne in časovne omejitve.Ura konfiguracije (DCLK) mora izpolnjevati meje frekvence (npr. Običajno do 10 MHz v standardnih serijskih načinih).Naprava zahteva kratko zamudo (približno 200 ms) po vklopu notranjega ponastavitve vklopa za stabilizacijo.Poleg tega morajo biti vsi konfiguracijski signali čisti, brez hrupa in pravilno končani.Če uporabljate vroče razpoke, je treba paziti, da zagotovite celovitost signala in pravilno zaporedje moči in V/I.

Prednosti EPF6016ATC144-2N

• Stroškovno učinkovit za modele srednje kompleksa

EPF6016ATC144-2N vzpostavlja ravnovesje med cenovno dostopnostjo in funkcionalnostjo, zaradi česar je idealen za modele, ki zahtevajo večjo prilagodljivost kot fiksna logika, vendar ne opravičujejo stroškov ali moči režijskih stroškov višjega cenovnega razreda FPGA.

• Poenostavljeno oblikovanje in integracija PCB

V primerjavi s FPGA z večjo gostoto, ki pogosto potrebujejo pakete BGA z drobnim višino, EPF6016ATC144-2N prihaja v standardnem 144-polnim paketu TQFP.Ta embalaža poenostavi oblikovanje in izdelavo PCB-jev, ker se izogne potrebam po naprednih orodjih za postavitev, mikrovijah ali dragih plošč z visokimi plastmi.Prav tako olajša ročno prodajo ali osnovno predelavo, kar je koristno za manjše ekipe ali laboratorije z omejenimi zmogljivostmi.

• Nizko tveganje za zastarelost med uvajanjem

Zaradi dolgotrajne podpore v zapuščenih industrijskih aplikacijah EPF6016ATC144-2N ostane na voljo na številnih sekundarnih trgih in je še vedno široko podprta v oblikovalski programski opremi, kot sta Quartus II in Max+Plus II.Za podjetja, ki vzdržujejo izdelke z dolgim lifestom, kot so tovarniška avtomatizacija, merilni sistemi ali telekomunikacijski moduli, to zagotavlja nadaljnji dostop do znanega silicija, ne da bi bilo treba preoblikovati strojno opremo okoli novejših, bolj zapletenih FPGA.

• Zanesljivo vedenje

Za razliko od nekaterih novejših visokozmogljivih FPGA, ki delujejo na tesnih robovih in so občutljivi na nihanja moči in temperature, je EPF6016ATC144-2N močan in strpen do skupnih okoljskih sprememb.Deluje udobno v komercialnem temperaturnem območju in podpira vroče sekanje, zaradi česar je zanesljiv v modularnih ali uporabnih sistemih.Ta zanesljivost je praktična izbira za sisteme, ki zahtevajo dosledno uspešnost skozi čas in v spremenljivih pogojih.

• Dolgoročna stabilnost oblikovanja

V scenarijih, kjer sta dolgoročna razpoložljivost in zamrznitev oblikovanja pomembnejša od vrhunskih zmogljivosti, je ta naprava trden kandidat.Ko je logika potrjena in konfiguracijska datoteka zaklenjena, lahko celoten sistem ostane nespremenjen dolga leta, tudi desetletja.To je velika korist pri vesoljskih, prevozu in vojaških aplikacijah, kjer je zahteva novih delov drago ali nepraktično.

Dimenzije embalaže EPF6016ATC144-2N

Vrsta paketa: TQFP-144 (tanek četrtcenski paket)

Velikost telesa: 20 mm × 20 mm

Pin nagib: 0,5 mm

Število pin: 144 zatičev

Višina paketa: 1,0 mm

Vrsta svinčevega okvirja: Galebno krilo vodi na vseh štirih straneh

Vrsta pritrditve: Površinska montacija (SMT)

Proizvajalec EPF6016ATC144-2N

EPF6016ATC144-2N je prvotno izdelal Altera Corporation, pionir pri razvoju nizov vrat, ki jih je mogoče vgraditi na terenu (FPGA).Leta 2015 je Altera pridobila Intel Corporation, in naprava je zdaj uradno navedena v Intelovi programirani skupini za rešitve, ki upravlja in podpira Alterove zapuščene linije izdelkov FPGA.Čeprav je EPF6016ATC144-2N del ukinjene družine, Intel ostaja formalni proizvajalec in skrbnik te naprave, pri čemer ohranja dokumentacijo, arhivirano podporo in obvestila o življenjskem ciklu pod blagovno znamko Intel.

Zaključek

EPF6016ATC144-2N je prilagodljiv in zanesljiv FPGA za številne različne projekte.Ponuja dobro količino logične moči, številne vhodne/izhodne zatiče in enostavne posodobitve v sistemu.Njegova zasnova podpira sisteme mešane napetosti, hitro gibanje podatkov in reprogramiranje, ne da bi ga odstranili s plošče.Pogosto se uporablja v stvareh, kot so kontrolni sistemi, obdelava signalov, komunikacijske povezave in opremo za testiranje.Z močno podporo, dolgo razpoložljivostjo in preprosto embalažo ostaja pametna izbira, ki potrebuje stroškovno učinkovito in stabilno rešitev.

PDF podatkovnega lista

EPF6016ATC144-2N podatkovni listi:

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Pogosto zastavljena vprašanja [FAQ]

1. Katera orodja potrebujem za programiranje danes EPF6016ATC144-2N?

Za razvoj in kompilacijo lahko uporabite Intelovo zapuščeno Quartus II ali Max+Plus II programsko opremo.Za programiranje orodja, kot sta USB-Blaster Cable in Quartus Programer, ostanejo združljiva za konfiguracijo.

2. Ali je EPF6016ATC144-2N primeren za majhne proizvodnje ali prototipiranje?

DA.Njegov paket TQFP-144 olajša prototip brez potrebe po naprednih orodjih za montažo.Prav tako je idealen za majhno proizvodnjo, kjer so potrebni nizki stroški in prilagodljivost.

3. Kako se EPF6016ATC144-2N v primerjavi z uspešnostjo primerja z novejšimi FPGA?

Čeprav ni tako bogat z značilnostmi kot sodobni višjega cenovnega FPGA, EPF6016ATC144-2N ponuja zanesljivo zmogljivost za zmerno logično zapletenost z nižjo porabo energije in enostavnejšo integracijo, zaradi česar je stroškovno učinkovita za številne aplikacije.

4. Ali je varno vroče vroče vklop ePF6016ATC144-2N v sistemih v živo?

DA.Ta FPGA podpira vroče sekljanje za sisteme 3.3V, kar omogoča vstavljanje ali odstranjevanje, ne da bi pri tem izklopilo gostiteljsko ploščo, idealno za terensko servis ali modularno oblikovanje strojne opreme.

5. Zakaj bi moral izbrati EPF6016ATC144-2N za rešitve ASIC ali CPLD po meri?

EPF6016ATC144-2N ponuja hitrejše razvojne cikle, reprogramiranje na terenu in znižane stroške vnaprej v primerjavi z ASIC.V primerjavi s CPLD -ji zagotavlja več logične zmogljivosti in prilagodljivega usmerjanja, idealnega za razširljive in razvijajoče se modele.

LC5768MC-75F256C CPLD: funkcije, specifikacije, prednosti in aplikacije

na 2025/07/10

Začetek z MC7447AHX1000NB

na 2025/07/10

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/19 147781

-

USB-C pinout in funkcije

na 2000/04/19 112062

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/19 111352

-

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/19 83816

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79629

-

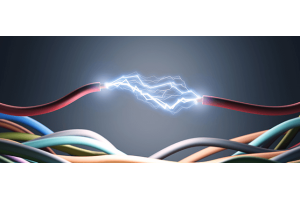

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66998

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63122

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63057

-

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54097

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52208