EPM7064STC100-7 CPLD: Funkcije, aplikacije in vodnik za programiranje v sistemu

EPM7064STC100-7 je močan čip iz Intelove serije Max® 7000S, zasnovan za ravnanje s kompleksnimi nalogami v elektronskih napravah.Ta priročnik obravnava glavne značilnosti in uporabe EPM7064STC100-7, kar poudarja njegovo sposobnost, da se lahko lažje reprogramira, hitro delovanje in prilagodljiv dizajn.Idealen za številne različne tehnologije, od majhnih pripomočkov do velikih industrijskih strojev, je ta čip ključni del za gradnjo naprednih digitalnih vezij.Katalog

Opis EPM7064STC100-7

The EPM7064STC100-7 je zapletena programabilna logična naprava (CPLD) iz Intelove serije Max® 7000S.Ima 64 makrocelic in 1.250 vrat, ki pomagajo pri gradnji zapletenih digitalnih vezij.Ta čip poteka z največjo hitrostjo 166,7 MHz, z zamudo signala 7,5 nanosekund (NS).Ima 68 vhodnih/izhodnih (V/I) zatičev, ki delujejo z logiko 3.3V in 5V, kar omogoča enostavno uporabo v različnih vezjih.Ključna značilnost je njegova programabilnost v sistemu 5.0V (ISP) prek vmesnika JTAG (IEEE 1149.1).To pomeni, da ga lahko reprogramirate, ne da bi ga odstranili iz vezja, kar olajšate testiranje in posodobitve.Na voljo je v 100-pinskem tankem četrtletju (TQFP), ki je kompakten paket, ki se nahaja na površini.Ta CPLD se uporablja za vgrajene sisteme, digitalno obdelavo signalov, komunikacijske naprave in industrijsko avtomatizacijo.

Nudimo kakovostne komponente in prilagojene storitve, zato je najbolje, da svoje naročilo v velikem obsegu oddate pri nas za zanesljive rešitve CPLD.

Funkcije EPM7064STC100-7

• Logika visoke gostote: EPM7064STC100-7 je zasnovan s 64 makrocelic in 1.250 uporabnimi vrati, zaradi česar je zelo primeren za izvajanje zapletenih logičnih funkcij v digitalnih vezjih.Ta arhitektura visoke gostote omogoča ustvarjanje zapletenih logičnih modelov, hkrati pa ohranja učinkovitost v programirljivih logičnih operacijah.Dobro optimizirana struktura makrocelice zagotavlja učinkovito uporabo razpoložljivih virov, ki podpira napredne kombinirane in zaporedne logične izvedbe.

• Hitra zmogljivost: EPM7064STC100-7, zgrajen za hitro obdelavo, deluje z največjo notranjo frekvenco 166,7 MHz, kar omogoča hitro izvajanje logičnih funkcij.Njegova zamuda s širjenjem 7,5 NS zagotavlja minimalno zamudo.Ta sposobnost hitrega preklopa izboljšuje zmožnost naprave za učinkovito obdelavo podatkov, kondicioniranje signalov in nadzorovanje nalog, zaradi česar je zanesljiva izbira za zahtevne digitalne sisteme.

• Vsestranski I/O: S 68 programirljivimi vhodnimi/izhodnimi zatiči EPM7064STC100-7 ponuja izjemno prilagodljivost za integracijo v različne modele vezja.Podpira logično raven 3.3V in 5V, omogoča brezhibno združljivost z različnimi sistemskimi napetostmi, kar odpravlja potrebo po dodatnih prestavkih na ravni napetosti.Ta prilagodljivost je primerna za aplikacije v mešani napetostni okolji, kar zagotavlja široko uporabnost v vgrajenih sistemih, industrijskih kontrolah in komunikacijskih omrežjih.

• Programabilnost v sistemu (ISP): Ena od prednosti EPM7064STC100-7 je njegova 5,0V programabilnost v sistemu (ISP), ki jo olajša prek IEEE STD.1149.1 JTAG vmesnik.Ta funkcija omogoča reprogramiranje in spreminjanje logičnih funkcij, ne da bi napravo ali fizično odstranili napravo, poenostavili vzdrževanje, odpravljanje napak in iterativni razvoj.Zmogljivost ponudnika internetnih storitev zmanjšuje izpadanje in poveča prilagodljivost posodobitev vdelane programske opreme, zaradi česar je neprecenljiva za dinamične in ponovno konfigurabilne digitalne modele.

EPM7064STC100-7 CAD modeli

Simbol EPM7064STC100-7

Odtis EPM7064STC100-7

EPM7064STC100-7 3D model

EPM7064STC100-7 blok diagram

The EPM7064STC100-7 blok diagram prikazuje, kako so logični elementi čipa povezani in nadzorovani.Ima štiri bloke logične matrike (laboratoriji), z oznako A, B, C in D, vsak pa vsebuje 16 makrocelic.Te makrocelice izvajajo logične funkcije in se povezujejo s programirljivim medsebojnim povezovalnim nizom (PIA), ki omogoča prilagodljivo usmerjanje signalov.Vsak laboratorij je povezan z V/I krmilnim blokom, ki obravnava do 16 vhodnih/izhodnih zatičev na laboratorij.Diagram prikazuje tudi globalne kontrolne signale (GCLK1, GCLK2, OE1 in GCLRN), ki pomagajo pri upravljanju funkcij ure in ponastavitve funkcij za čip.Nekatera logična vrata obdelujejo te signale, preden dosežejo različne dele sistema.Zasnova EPM7064STC100-7 omogoča uporabo v različnih programirljivih logičnih aplikacijah, kot so državni stroji, dekodiranje naslovov in druga digitalna vezja po meri.Njegove prilagodljive medsebojne povezave zagotavljajo učinkovit pretok signala in zanesljivo delovanje.

Specifikacije EPM7064STC100-7

|

Tip |

Parameter |

|

Proizvajalec |

Altera/Intel |

|

Serija |

MAX® 7000S |

|

Embalaža |

Pladenj |

|

Status dela |

Zastarelo |

|

Programirani tip |

V sistemskem programiranju |

|

Čas zamude TPD (1) Max |

7,5 ns |

|

Napajanje napetosti - notranja |

4.75V ~ 5.25V |

|

Število logičnih elementov/blokov |

4 |

|

Število makrocelic |

64 |

|

Število vrat |

1250 |

|

Število V/I. |

68 |

|

Delovna temperatura |

0 ° C ~ 70 ° C (TA) |

|

Vrsta pritrditve |

Površinski nosilec |

|

Paket / ohišje |

100-TQFP |

|

Paket dobaviteljskih naprav |

100-TQFP (14x14) |

|

Številka osnovnega izdelka |

EPM7064 |

EPM7064STC100-7 INSISTEM programiranja (ISP) zaporedje

EPM7064STC100-7, dela družine CPLD Max 7000S, sledi šeststopenjskemu zaporedju programiranja v sistemu (ISP), da se zagotovi pravilno konfiguracijo.Ta postopek vam omogoča, da napravo programirate, ne da bi jo odstranili s vezja.Postopek ponudnika internetnih storitev vključuje premik navodil, naslovov in podatkov s pomočjo TDI (testni podatki v) PIN med pridobivanjem odzivov prek zatiča TDO (testni podatki).

Prva faza, Vnesite ponudnika internetnih storitev, zagotavlja, da I/O zatiči nemoteno prehajajo iz uporabniškega načina v način ISP in zahteva približno 1 ms.Sledi Preverite ID, kjer se prebere silicijev ID naprave, da potrdi pravilni cilj.Naprej, Izbris v velikem obsegu Stopnja se premika v navodilih za brisanje in uporabi 100 ms brisanje impulza, ki očisti vse obstoječe podatke v celicah EEPROM.The Program Sledi stopnja, kjer se naslovi in podatki zaporedno preusmerijo v napravo, pri čemer uporabijo programske impulze za konfiguriranje celic EEPROM.Vsak naslov je treba programirati posamično, zaradi česar je ta korak zamuden glede na število celic EEPROM v napravi.

Ko je programiranje končano, Preveri Stage zagotavlja, da so bili podatki pravilno shranjeni.Tu se za celice EEPROM -a uporabijo bralni impulzi, pridobljeni podatki pa primerjamo s pričakovanimi vrednostmi.Če najdemo neskladja, bo morda potrebno reprogramiranje.Končno, Izhod ponudnika internetnih storitev Stage zagotavlja, da zatiči V/I prehajajo nazaj v uporabniški način, kar zahteva še 1 ms.Na skupni čas programiranja ali preverjanja vplivata dva glavna dejavnika: čas impulza, potreben za brisanje EEPROM, programiranje in prebrane operacije ter čas premika, ki je odvisen od frekvence TCK (testna ura) in števila ciklov, potrebnih za prenos navodil, naslovov in podatkov.Ker imajo različne naprave, ki so sposobne ISP, različno število celic EEPROM, so skupni fiksni in spremenljivi časi edinstveni za vsako napravo.Skupni čas ponudnika internetnih storitev se lahko izračuna kot funkcija frekvence TCK, števila ciljnih naprav in arhitekture EEPROM.

Aplikacije EPM7064STC100-7

Vgrajeni sistemi

EPM7064STC100-7 se široko uporablja v vgrajenih sistemskih aplikacijah, kjer služi kot prilagodljiva programabilna logična rešitev za nadzor različnih perifernih naprav, obdelavo signalov in izvajanje protokolov po meri.Njegova sposobnost vmešavanja z mikrokontrolerji in senzorji omogoča optimizacijo zmogljivosti sistema, hkrati pa ohranja kompakten odtis.S svojim hitrostjo in nizko porabo energije je odlična izbira za vgrajene aplikacije, ki zahtevajo zanesljivost in učinkovitost.

Digitalna obdelava signalov (DSP)

Pri digitalni obdelavi signalov ima EPM7064STC100-7 vlogo pri izvajanju filtrov, modulacije signala in različnih matematičnih funkcijah.Hitro preklopne hitrosti in nizka zamuda širjenja omogočajo, da je primerna za ravnanje z visokofrekvenčnimi nalogami obdelave podatkov, kar zagotavlja minimalno zamudo pri pretvorbi in manipulaciji s signalom.Običajno se uporablja v zvočni obdelavi, telekomunikacijah in radarskih sistemih.

Podatkovno komunikacijo

EPM7064STC100-7 se obsežno uporablja v sistemih za omrežje in podatkovno komunikacijo zaradi svoje sposobnosti ravnanja z logično intenzivnimi operacijami, kot so usmerjanje podatkov, medsebojno delovanje in popravljanje napak.Njegove programirljive zmogljivosti V/I omogočajo, da se prilagodi različnim komunikacijskim protokolom, zaradi česar je dragocena sestavina v Ethernet stikalih, usmerjevalnikih in telekomunikacijskih infrastrukturi.Njegova podpora za programirljivost v sistemu (ISP) omogoča tudi posodobitve na terenu, kar izboljšuje prilagodljivost v dinamičnih omrežnih okoljih.

Industrijska avtomatizacija

Industrijske aplikacije zahtevajo visoko zanesljivost, trajnost in nizko porabo energije, zaradi česar je EPM7064STC100-7 Najprimernejša izbira za programirljive logične krmilnike (PLC), sisteme za nadzor motorjev in avtomatizirano opremo za testiranje.S svojo programabilnostjo v sistemu, ki temelji na JTAG, omogoča izpopolnjevanje procesov avtomatizacije, ne da bi potrebovali fizično odstranitev ali preoblikovanje.Njegova vsestranskost v združljivosti napetosti je tudi primerna za povezovanje s široko paleto senzorjev in aktuatorjev, ki se uporabljajo v industrijskih nastavitvah.

EPM7064STC100-7 Podobni deli

Prednosti EPM7064STC100-7

Programiranost v sistemu (ISP)

Ena največjih prednosti EPM7064STC100-7 je njegova sposobnost, da se reprogramira, ko je še vedno nameščen v sistemu.To odpravlja potrebo po odstranitvi čipa za posodobitve, skrajša čas vzdrževanja in izboljšanje učinkovitosti.Spremembe oblikovanja lahko implementirate brez prekinitve proizvodnje, zaradi česar je stroškovno učinkovita rešitev za dolgoročne projekte.

Zmogljivost visoke hitrosti

Naprava podpira visoko notranjo delovno frekvenco do 166,7 MHz, kar omogoča hitro obdelavo podatkov in odzivne čase.Zaradi tega je idealno za aplikacije, ki zahtevajo obdelavo signalov, logični nadzor in visoko hitrost, kar zagotavlja bolj gladko in zanesljivejše delovanje sistema.

Vsestranska podpora V/I.

EPM7064STC100-7 ponuja prilagodljivost pri načrtovanju sistema z do 68 nastavljivimi V/I zatiči in združljivostjo z več napetostnimi stopnjami (3,3 V, 5V in strpnimi možnostmi za 2,5 V, 3,3V in 5V).Omogoča brezhibno integracijo v različna vezja in podpira mešano napetostno okolje, kar zmanjšuje težave z združljivostjo z drugimi komponentami.

Zanesljivo delovanje v okoljih

EPM7064STC100-7, zasnovan tako, da deluje v temperaturnem območju od 0 ° C do 70 ° C, zagotavlja dosledno in stabilno delovanje v različnih pogojih.Ta zanesljivost je najprimernejša izbira za aplikacije, kjer je potrebna okoljska stabilnost, kot so industrijska avtomatizacija, telekomunikacije in vgrajeni krmilni sistemi.

EPM7064STC100-7 Shema za pakete

EPM7064STC100-7 je CPLD (kompleksna programabilna logična naprava) iz serije Max 7000S Altera, nameščena v 100-pinskem tankem četrtletju, paketu (TQFP-100).Ta vrsta paketa je zasnovana za aplikacije, ki se nategnejo na površino, saj ponuja ravnovesje z visoko gostoto pin in kompaktne velikosti.The Diagram pin-out Sledi shema oštevilčenja v nasprotni smeri urinega kazalca, s pin 1, ki se nahaja v zgornjem levem kotu paketa.Če se premikate v nasprotni smeri urinega kazalca, prvih 25 zatičev zaseda levo stran, zatiči 26 do 50 so nameščeni vzdolž spodnjega roba, zatiči 51 do 75 se nadaljujejo vzdolž desne strani, zatiči 76 do 100 pa se porazdelijo vzdolž zgornjega roba.The Paket TQFP-100 Značilnosti se raztezajo navzven od vseh štirih strani ravnega, kvadratnega telesa.Ta zasnova izboljša združljivost na površini, hkrati pa ohranja ustrezen razmik za zatič za enostavno spajkanje in montažo.Vodilni nagib (razdalja med sosednjimi zatiči) je običajno 0,5 mm, kar optimizira celovitost signala, hkrati pa zmanjšuje celoten odtis.

Proizvajalec EPM7064STC100-7

EPM7064STC100-7 je CPLD (kompleksna programabilna logična naprava), ki jo je prvotno razvil Altera, polprevodniško podjetje, znano po svojih programirljivih logičnih rešitvah.V letu 2015, Intel Pridobljeno Altera, ki je vključil svoje linije izdelkov FPGA in CPLD v Intelovo programirljivo skupino rešitev (PSG).Od takrat je EPM7064STC100-7 blagovna znamka pod Intelom, čeprav je bila označena kot zastarela.Intel je kot proizvajalec ohranil zapuščinsko podporo za CPLD serije Max® 7000S, vključno s tem modelom, hkrati pa se je postopoma preusmeril v osredotočenost na sodobne FPGA in programirljive logične tehnologije.

Zaključek

EPM7064STC100-7 združuje zapletene funkcije, hitre zmogljivosti in enostavne posodobitve v enem čipu, kar dokazuje svojo vrednost v zahtevnih digitalnih nastavitvah.Ta vodnik je pokazal, kako deluje, za kaj se uporablja in kako se prilega različnim elektronskim sistemom.Pomaga, da naprave delujejo nemoteno in učinkovito, kar dokazuje, da je še vedno zelo uporabno za številne aplikacije.Ta vodnik ponuja jasen pogled na to, kako lahko EPM7064STC100-7 pomaga izboljšati elektronske modele in sistemske operacije.

PDF podatkovnega lista

EPM7064STC100-7 podatkovne liste:

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Pogosto zastavljena vprašanja [FAQ]

1. Kako je 7,5-odstotna zamuda širjenja EPM7064STC100-7 Udarna zmogljivost?

7,5-palčna zamuda za širjenje zagotavlja obdelavo signalov z nizko zamudo, zaradi česar je ta CPLD primeren za hitre aplikacije, kot so digitalna obdelava signalov (DSP), komunikacijski sistemi in industrijska avtomatizacija, ki zahteva natančen nadzor časa.

2. Ali je mogoče EPM7064STC100-7 programirati z uporabo sodobnih razvojnih orodij?

Da, lahko ga programiramo s pomočjo Intelove programske opreme Quartus II (prej Altera Quartus) skupaj z ustreznim programerjem JTAG.Vendar pa je podpora za starejše CPLD, kot je EPM7064STC100-7, v novejših različicah kvartusa omejena, zato boste morda morali uporabiti zapuščene različice, kot je Quartus II 13.0 SP1, ki še vedno podpirajo naprave serije Max® 7000S.

3. Ali EPM7064STC100-7 podpira mešano napetostno okolje?

Da, podpira tako 3.3V kot 5V logične ravni, zaradi česar je združljiv s široko paleto digitalnih vezij.Ta prilagodljivost je uporabna za povezovanje Legacy 5V komponent s sodobnimi 3,3V sistemi brez dodatnega vezja za premikanje nivoja.

4. Katera je najboljša metoda za odpravljanje težav z zasnovo EPM7064STC100-7?

Za odpravljanje težav lahko za spremljanje signalov uporabite Quartus SignalTap II logični analizator ali zunanje osciloskope in logične analizatorje.Če težave z odpravljanjem napak pri programiranju JTAG, zagotovite, da so povezave TDI, TDO, TCK in TMS pravilne in da uporabljate združljivi programer USB Blaster ali ByteBlasterMV.

5. Ali lahko programiram EPM7064STC100-7, ne da bi ga odstranil s svoje vezje?

DA.Programiranost v sistemu 5.0V (ISP) prek JTAG (IEEE 1149.1) vam omogoča reprogramiranje naprave, medtem ko ostane v sistemu.Zaradi tega so posodobitve vdelane programske opreme, odpravljanje napak in testiranje veliko učinkovitejše v primerjavi s tradicionalnimi CPLD.

Celoten vodnik za 10K upor: barvna koda, aplikacije in vezje

na 2025/03/10

Kondenzatorji v primerjavi z baterijami: Kaj je najbolje za vaše potrebe po energiji?

na 2025/03/7

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/19 147782

-

USB-C pinout in funkcije

na 2000/04/19 112062

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/19 111352

-

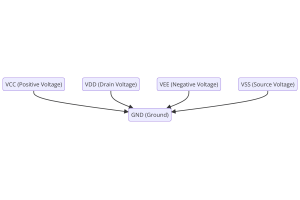

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/19 83819

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79639

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66999

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63124

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63062

-

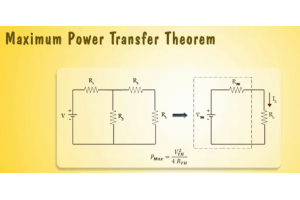

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54097

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52215