EPM7192SQC160-15 CPLD: funkcije, pinout, programiranje in aplikacije

Ta vodnik govori o EPM7192SQC160-15, programirljivem logičnem čipu iz družine Max 7000S.Pojasnjuje, kaj lahko naredi čip, kako deluje in kje ga je mogoče uporabiti.Pokaže, kako je čip vgrajen v notranjost, kaj počne vsak zatič in kako se poveže z drugimi deli.Vodnik vključuje tudi, kje je mogoče uporabiti ta čip, kako ga programirati korak za korakom, kakšni drugi podobni čipi obstajajo in kdo ga naredi.Katalog

Kaj je EPM7192SQC160-15?

The EPM7192SQC160-15 je CPLD srednjega razreda (kompleksna programirljiva logična naprava) iz družine Max 7000S, narejena za zanesljiv digitalni logični nadzor v vgrajenih in industrijskih sistemih.Ta čip ponuja 192 makrocelic in približno 3.750 logičnih vrat, kar zagotavlja dovolj zmogljivosti za ravnanje z zmernimi logičnimi nalogami.Vključuje 124 I/O zatičev in deluje na 5V napajanju, z multivolt V/I podporo za vmesnik tako s 3,3V kot 5V logičnimi sistemi.Njegova arhitektura, ki temelji na sistemu, ki temelji na sistemu, pomeni, da jo lahko reprogramirate neposredno v svojem vezju z uporabo JTAG, ne da bi potrebovali dodatne komponente ali zunanji pomnilnik.S hitrostjo –15 podpira sistemske frekvence ure do približno 76,9 MHz, kar ponuja hitro in dosledno časovno zmogljivost za široke digitalne aplikacije.Družina Max 7000S je znana po svojih trdnih zmogljivostih, pomnilniku EEPROM in prilagodljivih napetosti.

Iščete EPM7192SQC160-15?Pišite nam, da preverite trenutne zaloge, čas svinca in cene.

EPM7192SQC160-15 CAD modeli

Simbol EPM7192SQC160-15

Odtis EPM7192SQC160-15

EPM7192SQC160-15 3D model

Funkcije EPM7192SQC160-15

192 Makrocelice: Naprava vključuje 192 makrocelic, ki služijo kot temeljni programirljivi elementi.Te makrocelice je mogoče konfigurirati za izvajanje najrazličnejših kombiniranih in zaporednih logičnih funkcij, potrebnih pri digitalnih modelih.

Približno 3.750 logičnih vrat: Ponuja enakovredno logično zmogljivost približno 3.750 vrat, zaradi česar je primerna za srednje kompleksno krmilno logiko, državne stroje ali logiko lepila v vgrajenih sistemih.

Programiranost v sistemu prek JTAG: Ima pomnilnik na osnovi EEPROM, ki omogoča reprogramiranje neposredno znotraj sistema s standardnim vmesnikom JTAG, ki podpira standarde IEEE 1149.1 in IEEE 1532.

Največja frekvenca do 125 MHz: Notranja logika lahko deluje s hitrostjo ure, ki dosežejo 125 MHz, kar omogoča hitro obdelavo za časovno občutljive aplikacije.

Zamuda širjenja 7,5 ns: Čip ponuja nizko razmnoževanje približno 7,5 nanosekund, kar zagotavlja hiter odziv signala od vhoda do izhoda.

Podpira 5V oskrbo z multivolt V/I: Naprava deluje na 5V jedrni in podpira večvoltni V/I, kar omogoča združljivost z nivojem signala 5V in 3.3V za enostavno integracijo v sisteme mešane napetosti.

Programabilna hitrost SLOW in izhodi z odprtim odtokom: Za zmanjšanje EMI lahko nadzorujete hitrost roba signala in izberete izhode z odprtim odtokom za žično-logiko ali prestavljanje ravni.

Šest globalnih izhodov omogoča signale: Ti globalni kontrolni signali omogočajo omogočanje ali onemogočanje izhodov v več bankah V/I za učinkovito upravljanje signalov.

Konfigurabilni prelivi v makrocelici: Vsaka makrocela vključuje flip-flop, ki podpira prednastavitev, jasen, omogočen in individualni nadzor, ki zagotavlja večjo prilagodljivost za zaporedno logično zasnovo.

Način z nizko močjo: Naprava vključuje funkcijo varčevanja z močjo, ki lahko zmanjša porabo energije makrocelic za več kot 50%, kar je koristno za energetsko učinkovite aplikacije.

JTAG mejna preskusna podpora : Naprave z 128 ali več makrocelic, kot je ta, vključujejo funkcije testiranja polne meje za učinkovito diagnostiko in potrjevanje na ravni plošče.

Varnostni bit za zaščito pred oblikovanjem: Programirani varnostni bit zagotavlja, da notranje zasnove ni mogoče brati ali kopirati, kar ščiti intelektualno lastnino.

PCI-združljiv I/O.: Struktura V/I je zasnovana tako, da izpolnjuje električne zahteve PCI, kar omogoča neposredno povezovanje s sistemi, ki temeljijo na PCI.

Delovno temperaturno območje od 0 ° C do 70 ° C: Standardni temperaturni razpon komercialnega razreda naredi ta naprava primerna za večino notranjega in nadzorovanega okolja.

EPM7192SQC160-15 Diagram pinout

Ta diagram prikazuje postavitev PIN za EPM7192SQC160-15 in podobne naprave Altera Max 7000S.Čip ima 160 zatičev, razporejenih okoli vseh štirih strani v kvadratnem paketu QFP.Pin 1 se začne v zgornjem levem kotu in številke gredo v nasprotni smeri urinega kazalca okoli čipa.Vsaka stran ima 40 zatičev.Majhna pika na zgornjem levem oznakah pin 1, ki pomaga pri pravilni namestitvi.Ime čipa v središču kaže, da je združljivo z drugimi modeli v isti družini.Ta postavitev zagotavlja številne V/I povezave in je uporabna za zapletene logične zasnove.

Max 7000s blok diagram

Ta blok diagram prikazuje notranjo strukturo CPLD Max 7000S, vključno z EPM7192SQC160-15.Čip je razdeljen na štiri glavne odseke, imenovane logični niz blokov (laboratorij A do D).Vsak laboratorij ima 16 makrocelic, ki so majhne logične enote, ki se uporabljajo za gradnjo digitalnih vezij.Ti laboratoriji skupaj obravnavajo zapletene logične operacije.

V središču je programirljivi medsebojni niz (PIA), ki povezuje vse laboratorije in jim omogoča, da delijo podatke.Vsak laboratorij pošlje in sprejema signale prek 36 kanalov, kar daje fleksibilno usmerjanje med logičnimi bloki.Okoli robov obstajajo krmilni bloki V/I, ki povezujejo 6 do 16 v/I zatičev na vsak laboratorij, kar omogoča, da se napravi poveže z drugimi deli sistema.

Na vrhu so prikazani globalni krmilni signali, kot so ure in izhodne omogočene.Ti signali pomagajo upravljati, kako se podatki gibljejo znotraj čipa in kdaj so aktivni izhodi.Na splošno diagram prikazuje, kako EPM7192Sqc160-15 organizira svojo logiko in povezave za podporo digitalnim modelom po meri.

Specifikacije EPM7192SQC160-15

|

Tip |

Parameter |

|

Proizvajalec |

Altera |

|

Serija |

MAX® 7000S |

|

Embalaža |

Pladenj |

|

Status dela |

Zastarelo |

|

Programirani tip |

V sistemskem programiranju |

|

Čas zamude TPD (1) Max |

15 ns |

|

Napajanje napetosti - notranja |

4.75V ~ 5.25V |

|

Število logičnih elementov/blokov |

12 |

|

Število makrocelic |

192 |

|

Število vrat |

3750 |

|

Število V/I. |

124 |

|

Delovna temperatura |

0 ° C ~ 70 ° C (TA) |

|

Vrsta pritrditve |

Površinski nosilec |

|

Paket / ohišje |

160-bqfp |

|

Paket dobaviteljskih naprav |

160-PQFP (28x28) |

|

Številka osnovnega izdelka |

EPM7192 |

EPM7192SQC160-15 aplikacij

Vgrajena logika sistemskega lepila

EPM7192SQC160-15 je idealen za premostitev različnih digitalnih naprav v vgrajenih sistemih.Uporablja se lahko za upravljanje komunikacije med mikrokontrolerji, pomnilniškimi čipi in V/I napravami z ravnanjem z dekodiranjem naslovov, nadzorom avtobusa in prilagoditvami časa, ne da bi potrebovali diskretne logične IC.

Državni stroji in logika nadzora

S svojimi makroceli iz 192 je čip zelo primeren za izvajanje državnih strojev po meri in logiko nadzora.Običajno se uporablja pri avtomatizacijskih nalogah, motoričnih krmilnikih in krmilnih sistemih, ki temeljijo na časovnih mestih, ki zahtevajo zanesljive in ponovljive prehode stanja.

Vmesniki komunikacijskega protokola

Ta CPLD lahko programiramo tako, da ustvarite ali prevedete komunikacijske protokole, kot so UART, SPI, I²C ali serijski formati po meri.Omogoča enostavno konfiguracijo in spreminjanje brez spreminjanja strojne opreme, zaradi česar je dragocena za komunikacijsko povezovanje.

Predobdelava digitalnega signala

Zahvaljujoč hitri logični hitrosti in nizki zamudi širjenja lahko obravnava preproste naloge obdelave signalov, kot so filtriranje, multipleksiranje ali zaznavanje robov, preden signali dosežejo glavni procesor ali čip DSP.

Prevajanje vmesnika in prestavljanje ravni

Njegova multivoltna V/I sposobnost podpira tako 3.3V kot 5V signale.Zaradi tega je primeren za modele, ki vključujejo komponente, ki delujejo na različnih napetostnih nivojih, kar omogoča varen in učinkovit prevajanje napetosti.

Posodobitve hitrega prototipov in v sistemu

Ta čip lahko uporabite v sistemih, ki morda zahtevajo pogoste logične posodobitve.Njegova struktura, ki temelji na EEPROM-u in programski vmesnik JTAG, omogočata reprogramiranje logike tudi po sestavljanju plošče.

Test in diagnostika na ravni plošče

S podporo mejne skeniranja prek JTAG preizkuša povezave med čipi na PCB, ne da bi potrebovali sonde.To je koristno med proizvodnjo in diagnostiko na terenu za odkrivanje težav s spajkanjem ali usmerjanjem.

EPM7192SQC160-15 Podobni deli

• EPM7192EQC160-20 (Altera)

Ta naprava je iz iste serije Max 7000 in ponuja enake logične vire, 192 makrocelic in 124 V/I zatičev v paketu PQFP 160-polni.Deluje s počasnejšo hitrostjo –20, kar pomeni, da ima daljše zamude širjenja (~ 20 ns), vendar še vedno ustreza potrebam ne-časovnih kritičnih modelov.To je primerna alternativa za aplikacije, kjer je logična gostota pomembna, vendar ultra hitri čas ni prednostna naloga, zato je idealen za stroškovno občutljive projekte, ki še vedno potrebujejo funkcionalno enakovrednost.

• EPM7192SQI160-10N (Altera)

Ta del je tudi logično združljiv z EPM7192SQC160-15, ki ponuja enako število makrocelic in V/OS.Vendar uporablja oceno hitrosti –10, ki podpira hitrejše delovanje z izboljšanim časovnim razporedom (10 ns zamuda za širjenje).Prav tako podpira podaljšano temperaturno območje od –40 ° C do +85 ° C, zaradi česar je odličen nadomestek za industrijske ali zunanje aplikacije.To je idealno, kadar je potrebna večja hitrost in odpornost na okolje.

• EPM7192SQC160-7 (Intel)

Kot neposredna različica EPM7192SQC160-15 različica –7 prinaša najhitrejšo zmogljivost v družini, širjenje pa se zmanjša na 7,5 ns.Ohranja isto konfiguracijo PIN-a, specifikacije napajanja in logično gostoto, kar ponuja zamenjavo za tiste, ki iščejo boljšo hitrost, ne da bi spremenili postavitev plošče ali napetostne zahteve.Zaradi tega je najboljša izbira za časovne kritične modele, ki potrebujejo hitrejši odziv signala, medtem ko ostanejo v istem oblikovalskem odtisu.

EPM7192SQC160-15 koraki programiranja

1. Vnesite način ISP

Prvi korak je preusmeritev naprave v način ISP (programiranje v sistemu).To se naredi prek vmesnika JTAG.Enkrat v načinu ponudnika internetnih storitev so vsi V/I zatiči na napravi nameščeni v varen tridržavni način, da se prepreči nenamerne logične motnje med programiranjem.Ta inicializacija običajno traja približno 1 milisekund.

2. Preverite ID naprave

V napravo je vgrajen edinstven silicijev ID, da preveri, da je pravi model, preden se začne programiranje.Sistem se preusmeri v navodilo za branje in pridobi ID prek vrstice TDO (testni podatki).Ta preverjanje zagotavlja, da je programsko orodje povezano z desnim CPLD in se izogne napakam, kot je prepisovanje drugega dela.

3. Izbris v velikem obsegu

V velikem obsegu izbriše vse prej shranjene podatke v pomnilniku EEPROM CPLD.To pripravi čip na prejeto novo konfiguracijo.Ukaz ERASE sproži impulz, ki običajno traja približno 100 milisekund, in zagotovi, da se ponastavijo vse programirljive celice.

4. Program EEPROM

Novi konfiguracijski podatki se naložijo v napravo s premikanjem naslovov in podatkovnih bitov skozi vrata JTAG.Vsaka pomnilniška celica je napisana ena za drugim, s programiranjem impulza, ki se uporablja po vsakem uspešnem ciklu pisanja.Ta postopek določa logično strukturo, ki jo bo CPLD uporabljal pri napajanju.

5. Preverite EEPROM

Po programiranju naprava izvede korak preverjanja.To vključuje branje vsake programirane lokacije pomnilnika in primerjavo izhodnih vrednosti s predvidenimi podatki.Če preverjanje ne uspe, je treba postopek ponoviti.Ta korak zagotavlja, da je bila konfiguracija uspešno napisana.

6. Način izstopa ISP

Ko je preverjanje končano, se izda končni ukaz za izhod iz iSp načina.Naprava ponovno aktivira zatiče v/I in nadaljuje z normalnim delovanjem.Ta prehod traja tudi približno 1 milisekund in zaključi cikel programiranja v sistemu.

EPM7192SQC160-15 Dimenzije embalaže

• Velikost telesa: 28 mm × 28 mm

• Višina paketa: 3,4 mm

• Pin nagib: 0,65 mm

EPM7192SQC160-15 Proizvajalec

EPM7192SQC160-15 je prvotno izdelal Altera Corporation, podjetje, znano po svojih naprednih programirljivih logičnih napravah.Leta 2015 je Altera pridobila Intel Corporation, in naprava je zdaj del Intelove programirljive skupine za rešitve v okviru družine CPLD Max 7000S.Intel še naprej podpira zapuščene izdelke Altera, čeprav je EPM7192SQC160-15 zdaj v večini uradnih katalogov uvrščen med zastarele.Kljub ukinjenemu statusu, Intelov zgodovinski ugled za zanesljivost in Alterova zapuščina v logičnih rešitvah z visoko zmogljivostjo zagotavljata nadaljnje povpraševanje in razpoložljivost s sekundarnimi distributerji.

Zaključek

EPM7192SQC160-15 je uporaben in prilagodljiv čip za ravnanje z digitalnimi krmilnimi nalogami v številnih elektronskih sistemih.Ponuja dovolj logične moči za delovna mesta, kot so gradnja državnih strojev po meri, ravnanje s signali in povezovanje različnih naprav.Podpira različne napetostne ravni, deluje s hitrimi hitrostmi in ga je mogoče enostavno posodobiti prek JTAG.Njegova notranja zasnova omogoča nemoten pretok signala in enostavne spremembe logike.Čeprav je zdaj ukinjen, je to še vedno odlična možnost za stare ali tekoče projekte in ga je mogoče nadomestiti s podobnimi čipi, ki ponujajo hitrejšo ali širšo temperaturno podporo.

PDF podatkovnega lista

EPM7192SQC160-15 podatkovne liste:

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Pogosto zastavljena vprašanja [FAQ]

1. Ali lahko programiram EPM7192SQC160-15, ne da bi ga odstranil s vezje?

Da, čip podpira programiranje v sistemu (ISP) prek vmesnika JTAG, tako da ga lahko programirate ali reprogramirate neposredno, medtem ko je spajkan na PCB, ki poenostavi posodobitve oblikovanja in zmanjša predelavo.

2. Katero programsko opremo za programsko opremo naj uporabim za EPM7192SQC160-15?

Za ustvarjanje logičnih modelov, sestavljanje kode in upravljanje postopka programiranja, ki temelji na JTAG, lahko uporabite programsko opremo Altera's Quartus II (starejše različice).Quartus II podpira naprave Max 7000S, kot je EPM7192SQC160-15.

3. Ali EPM7192SQC160-15 potrebuje zunanji pomnilnik za delovanje?

Ne, ima notranji konfiguracijski pomnilnik na osnovi EEPROM.Vsa logična konfiguracija je shranjena znotraj čipa, zato za shranjevanje logičnih stanj ali zaporedja zagona ni potreben zunanji pomnilnik.

4. Kaj naredi EPM7192SQC160-15 primeren za industrijsko uporabo?

Njegova robustna operacija 5V, večvoltna združljivost V/I, hitra logična obdelava in nehlapni pomnilnik, ki temelji na EEPROM, omogočajo zanesljivo za industrijske sisteme, ki zahtevajo stabilne in trajne digitalne logične funkcije.

5. Kako EPM7192SQC160-15 roči mešane napetostne sisteme?

Zahvaljujoč multivolt V/I podpori lahko naprava povezuje tako s 3,3V kot 5V logično raven, zaradi česar je idealna za sisteme mešanega signala in povezovanje s sodobnimi komponentami z nizko napetostjo.

Zakaj za svoj projekt izbrati EPF10K100EFC484-3

na 2025/06/13

Kaj je stikalo SPST in kako deluje?

na 2025/06/12

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/18 147766

-

USB-C pinout in funkcije

na 2000/04/18 111994

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/18 111351

-

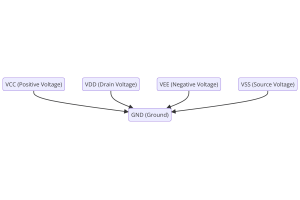

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/18 83755

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79550

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66951

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63094

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63028

-

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54094

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52176