HDL: Odklepanje inovacij v digitalnem vezju

Ta priročnik raziskuje opis strojne opreme (HDL), pomembna orodja za pretvorbo abstraktnih modelov v resnična, izdelana vezja.Zajemamo njihovo evolucijo, aplikacije v oblikovanju ASIC in FPGA ter njihov vpliv na sodobno elektroniko.S pomočjo primerov in strokovnih vpogledov je ta vodnik poglobiti vaše razumevanje HDL -jev in okrepiti tako vašo teorijo kot praktične veščine.Odkrijte, kako HDLS premosti vrzel med idejami in fizičnimi napravami, ki vodijo inovacije v tehnologiji.Katalog

Vloga HDL v digitalnem dizajnu

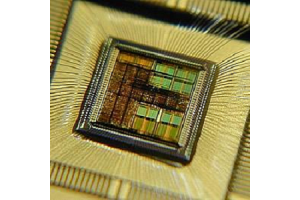

Jezik opisa strojne opreme (HDL) ima vlogo pri oblikovanju digitalnih sistemov z zagotavljanjem strukturiranega načina za modeliranje kompleksnih vezij.Omogoča razgradnjo velikih sistemov na manjše, obvladljive module, ki so testirani in preverjeni z orodji za avtomatizacijo elektronske zasnove (EDA).Ko so potrjeni, se ti moduli sintetizirajo v mreže na ravni vrat in se skozi umestitev in usmerjanje ASIC ali FPGA pretvorijo v fizična vezja.HDL, ki se široko uporablja v panogah, kot je Silicijeva dolina, poganja inovacije, tako da pomaga omejitvam ravnotežja z ustvarjalnimi rešitvami, zaradi česar je ključna sestavina pri napredovanju digitalne tehnologije.

Zgodovinski razvoj HDL

Razvoj jezikov za opis strojne opreme (HDL) sega desetletja, ki se razvija od razdrobljenih, nišnih orodij v standardizirane, celotne industrije, kot sta VHDL in Verilog, do konca osemdesetih let prejšnjega stoletja.Te standardizirane HDL -jeve enotne oblikovalske prakse in izboljšano sodelovanje.Ko je tehnologija napredovala, se je HDLS razširil tako, da bi podpiral bolj zapletene sisteme, premoščanje strojne in programske opreme z novimi jeziki, kot sta SystemC in Superlog.HDLS je pokazal svojo vrednost pri izboljšanju komunikacije, zmanjšanju napak in racionalizaciji procesa oblikovanja.Nenehna evolucija HDL -jev odraža potrebo po nenehnih inovacijah, da bi ustrezali spreminjajočim se zahtevam digitalnega oblikovanja za sodobni razvoj tehnologije.

Namen

Ker so integrirana vezja postala bolj zapletena, ki jo je od sedemdesetih let prejšnjega stoletja poganjal Mooreov zakon, so se oblikovalske metodologije preusmerile od osredotočanja na posamezne komponente na upravljanje pretoka in časovne razporeditve na ravni sistema.Ta premik je privedel do sprejetja abstrakcije na ravni prenosa registra (RTL), ki omogoča osredotočanje na logične funkcije in čas, ne da bi se morali zgodaj obravnavati.RTL abstrakcija, podprta z jeziki opisa strojne opreme (HDL), poenostavi postopek oblikovanja z uravnoteženjem zmogljivosti, moči in razširljivosti.Zmanjšuje cikle oblikovanja, povečuje sodelovanje in pomaga predvideti morebitna vprašanja, kar preprečuje drage revizije.Z osredotočanjem na višje stopnje abstrakcije odklenete večjo učinkovitost, prilagodljivost in inovacije v hitro razvijajoči se tehnološki pokrajini.

Strukturne značilnosti

Opis strojne opreme Jeziki (HDL) služijo kot besedilni okviri, ki opredeljujejo strukturo, vedenje in čas vezja.Delujejo kot vzporedni programski jeziki, vendar so posebej usmerjeni v upravljanje časovnih in strojnih povezav.HDL delujejo na različnih ravneh abstrakcije, strukturnih, vedenjskih in registrskih prenosov, da se približajo oblikovanju vezja z različnih vidikov.Na strukturni ravni so HDLS podrobne komponente in povezave, podobne shemam.Stopnja vedenja se osredotoča na to, kar bi moralo storiti vezje, medtem ko raven prenosnih registra (RTL) opisuje pretok podatkov in operacije med registri, uravnoteženjem funkcionalnosti in specifikami strojne opreme.HDL podpirajo tudi logično sintezo, pretvorbo modelov na visoki ravni v vezja na ravni vrat in simulacijo, ki preizkuša funkcionalnost pred uvajanjem strojne opreme.Za razliko od tradicionalnih programskih jezikov HDL -ji predvsem modelirajo orodja, ki zajemajo strojno vedenje, zaradi česar so pomembni za natančno, inovativno oblikovanje vezja.

Raziskovanje pretoka podatkov v HDL

Za razliko od tradicionalnih programskih jezikov, ki dajejo prednost kontrolnemu toku, se HDL osredotočajo na modeliranje pretoka podatkov in čas v vezjih za razvoj in simulacijo strojne opreme.Ta edinstvena sposobnost zajemanja časovnega vedenja strojne opreme nastavi HDL, razen jezikov, kot je C ++.Sodobni HDL, kot je SystemVerilog, vse bolj mešajo programske paradigme, ki vključujejo objektno usmerjene koncepte za izboljšanje modularnosti in vzdrževanja v zapletenih sistemih.HDL igrajo tudi vlogo pri logični sintezi, ki prenaša opise na visoki ravni v izvedbe na ravni vrat in tako zagotavlja, da se abstraktni modeli uskladijo s fizikalnimi omejitvami.Poleg tega se za simulacijo in preverjanje pred proizvodnjo uporabljajo ne-sintezabilni elementi HDL za simulacijo in preverjanje.Ko se HDL še naprej razvijajo, bodo verjetno sprejemali več programske funkcije za reševanje naraščajočih kompleksnosti strojne opreme in premostili vrzel med natančnostjo strojne opreme in prijazno abstrakcijo.

Izboljšanje integriranega vezja s HDL

Opis strojne opreme Jeziki (HDLS) racionalizirajo zapleten postopek oblikovanja integriranih vezij s preoblikovanjem abstraktnih idej v praktične, izvedljive načrte.Mnogi pogosto uporabljajo diagrame tokov in državne diagrame, da preslikajo logiko vezja, preden jo pretvorijo v natančno kodo HDL, podobno kot ustvarjanje načrtov za gradnjo.Medtem ko se držijo zahtev v vezju, drugi prinašajo svoj edinstven slog kodiranju z vključitvijo algoritmov in scenarijem za poenostavitev ponavljajočih se nalog.Orodja za preverjanje napak nato zgodaj prepoznajo težave in tako zagotovijo zanesljivost pred sintezo.Po sintezi so netlisti pripravljeni na proizvodnjo, bodisi za FPGA ali ASIC, s poudarkom na specifikacijah naprav, da se izognemo proizvodnim izzivom.HDLS vzpostavi ravnovesje med ustvarjalnostjo in natančnostjo, kar omogoča inovativne, a zanesljive modele vezja, ki učinkovito napredujejo od koncepta do fizične realizacije.

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Vitis Unified Software Platform: pospeševanje vdelanih sistemov in prilagodljivo računalništvo z Xilinxom

na 2025/01/7

Evolucija in strateški napredek v tehnologiji VLSI

na 2025/01/6

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/18 147780

-

USB-C pinout in funkcije

na 2000/04/18 112050

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/18 111352

-

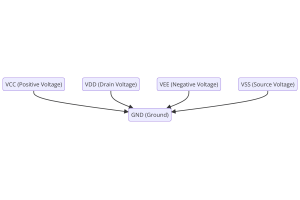

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/18 83806

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79608

-

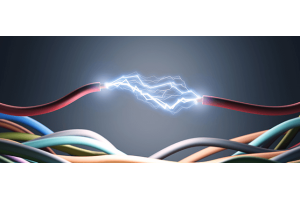

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66988

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63113

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63049

-

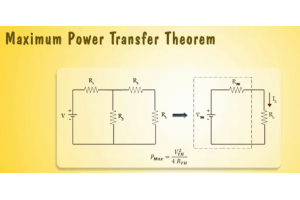

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54097

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52199