Prekinitvena vektorska tabela: arhitektura, upravljanje in aplikacije

Ta priročnik raziskuje prepletno vektorsko tabelo, komponento računalniške arhitekture, ki povezuje prekinitve strojne opreme z odzivi na programsko opremo.Z razumevanjem, kako se upravljajo prekinitve, lahko vidimo, kako sistemi nemoteno ravnajo z nalogami, od rutinskih operacij do nujnih primerov.Ogledali si bomo, kako pretekle metode oblikujejo trenutne prakse in kako ti mehanizmi vplivajo na delovanje in zanesljivost sodobnega računalništva.Pridružite se nam, ko razkrijemo pomen te teme tako v teoriji kot v aplikacijah.Katalog

Prekinitev vektorske tabele

Razumevanje identifikacije virov prekinitve je pomembno za določitev vhodnega naslova ustrezne rutine prekinitve, splošno znane kot prekinitveni vektor.V PC/AT Architecture ta postopek pomaga z ustvarjanjem kode za prekinitev, imenovano število prekinitve, ki lahko izvira iz različnih virov, na primer neposredno kodirano v navodilo ali samodejno ustvarjen s strani CPU -ja.Med postopkom prekinitve odziva na 8259A programirljivo krmilnik prekinitve (PIC) prinaša številko prekinitve, ki ustreza prekinitvi najvišjega prioriteta, ki zahteva takojšnjo pozornost.Ta prednostna naloga zagotavlja, da nujne naloge prejemajo pravočasno storitev, kar odraža širše načelo učinkovitega dodeljevanja virov pri zasnovi sistema.Matematični odnos, ki ureja ta postopek, je preprost: Številka prekinitve, pomnožena s štirimi, dobi začetni naslov prekinitvenega vektorja, iz katerega naslednje štiri pomnilniške enote zagotavljajo vstopno točko do rutine prekinitve.Ta strukturiran pristop ne samo povečuje učinkovitost ravnanja z prekinitvami, ampak tudi kaže na pomen sistematične organizacije pri računalništvu.V praksi je razumevanje tega odnosa neprecenljivo za odpravljanje napak in optimizacijo, saj lahko sledenje prekinitvah vektorjev pomaga razkriti ozka grla ali neučinkovitost znotraj servisnih rutin.Sodobne arhitekture operacijskega sistema pogosto vključujejo podobna načela prednostne naloge in prekinitve upravljanja, kar poudarja njihovo vlogo pri ohranjanju uspešnosti sistema.Preprečenosti tabele prekinitve vektorja poudarjajo dinamično medsebojno delovanje med strojno in programsko opremo pri upravljanju sistemskih virov, kar razkriva premišljeno zasnovo za ustvarjanje odzivnih in zanesljivih računalniških okoljev.

Uvod

Vstopna točka za program prekinitve je zapleteno opredeljena s kombinacijo odmika in osnovne vrednosti segmenta.Vsak prekinitveni vektor zaseda 4 bajte pomnilnika, kar odraža pomemben vidik, kako arhitektura 8086 spretno upravlja tako s strojno in programsko opremo.Prekinitvena vektorska tabela, ki je v najnižjih 1kb sistemskega pomnilnika 8086, služi kot skladišče.Shranjuje 256 prekinitvenih vektorjev, natančno organiziranih v naraščajočem vrstnem redu na podlagi številke prekinitve.

Med prekinitvenim dogodkom CPU prevzame vlogo pri določanju lokacije ustreznega prekinitvenega vektorja znotraj te tabele.To določitev vodi številka prekinitve, ki je bila prejeta iz vmesniškega vezja.Takšen postopek ne prikazuje samo učinkovitosti arhitekture CPU-ja, ampak tudi poudarja dobro strukturiran mehanizem za obdelavo prekinitve.Pridobivanje prekinitvenega vektorja omogoča nemoten preusmeritev CPU -ja za nemoteno preusmeritev programa na ustrezno rutino prekinitve, s čimer zagotovi, da sistem hitro reagira na različne dogodke.

Razumevanje nianse tega procesa je mogoče močno obogatiti z upoštevanjem praktičnih aplikacij.Na primer, možnost hitrega dostopa in izvajanja rutin prekinitve lahko pomeni razliko med uspehom in neuspehom.Zasnova prekinitvene vektorske tabele olajša sistematično metodo za upravljanje več vrst prekinitev, kar je še posebej dobro v okoljih, kjer ima čas in zanesljivost veliko teže.

Odvisnost arhitekture od določene odmične in segmentne osnovne vrednosti prikazuje širše načelo v računalništvu: ravnovesje med strukturo in prožnostjo.To ravnotežje odmeva s temami v zasnovi programske opreme, kjer dobro definirani vmesniki in protokoli prispevajo k razvoju bolj vzdržljivih in razširljivih sistemov.Analiza, kako 8086 upravlja prekinitve, omogoča, da vzpostavi vzporednice s sodobnimi sistemi, ki še naprej rastejo v zapletenosti in sposobnosti, vendar še vedno nagibajo na načela, ki so bila določena pred desetletji.

Vektorska tabela arhitekture 80x86

Arhitektura 80x86 zapleteno organizira vse prekinitvene vektorje v določenem pomnilniškem območju in tvori tisto, kar se imenuje tabela vektorja prekinitve.Ta tabela je sistematično razporejena na podlagi številk prekinitve, ki dejansko deluje kot imenik vhodnih naslovov za rutine prekinitve storitev (ISR).Ta tabela ni fiksna entiteta, ima sposobnost dinamično spreminjanja na ravni operacijskega sistema, kar ima za posledico velike razlike v različnih sistemih.Ta prirojena fleksibilnost poudarja sposobnost arhitekture, da se prilagodi številnim operativnim zahtevam in konfiguracijam strojne opreme.

Primarna funkcija prekinitvene vektorske tabele je omogočiti učinkovito obvladovanje prekinitev, ki se uporabljajo za ravnanje z asinhronimi dogodki.Vsak vnos znotraj tabele ustreza določeni vrsti prekinitve, kar omogoča, da CPU hitro prepozna ustrezen ISR, ko se pojavi prekinitev.Ta mehanizem je pomemben za vzdrževanje odzivnosti sistema, zlasti v scenarijih, kjer več procesov ali niti za vire CPU -ja.

Sposobnost dinamičnega posodabljanja prekinitvene vektorske tabele je ključna funkcija, ki pomaga operacijskim sistemom izboljšati zmogljivost in učinkoviteje upravljati vire.Na primer, ko je dodana nova naprava, lahko operacijski sistem posodobi tabelo z novimi upravljavci prekinitve, ne da bi potrebovali ponovni zagon sistema.Ta prilagodljivost odraža naraščajoč poudarek v sodobnem računalništvu na prilagodljivosti in razširljivosti.

Intel Rezervira 32 Prekinitvenih številk (0x00 do 0x1f) za zaščiten način CPU, ki obravnavajo sistemske dogodke, kot so napake, ki so delile ničle ali neveljaven dostop pomnilnika.V Linuxu se sistem prekinijo pri 0x20, pri čemer jih ločijo od rezerviranih prekinitev.Ta ločitev poudarja pomen strukturiranega pristopa k upravljanju prekinitev.Na primer, prekinitev ponastavitve za čip 8259 je dober del Linuxovega sistema za prekinitev prekinitve, ki pomaga operacijskemu sistemu, da se učinkovito okreva od napak.

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Načela in aplikacije klasične teorije testov (CTT)

na 2024/12/31

Vloga vgrajene tehnologije za samotest (BIST) v sodobni elektroniki

na 2024/12/30

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/18 147776

-

USB-C pinout in funkcije

na 2000/04/18 112018

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/18 111351

-

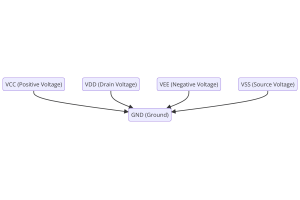

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/18 83777

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79575

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66964

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63104

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63041

-

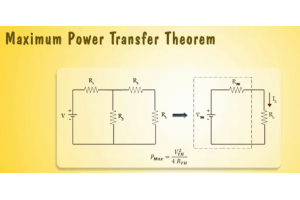

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54097

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52189