Zaporedna logika: načela, naprave, izzivi in metode inšpekcijskih pregledov

Ta vodnik raziskuje zaporedna logična vezja, ki razbije njihova načela, vrste in uporabe.Pojasnjuje, kako pomnilnik in logika delujeta skupaj, zaradi česar so ta vezja pomembna v sodobnih digitalnih sistemih.Spoznali boste števce, registre in generatorje impulzov, pa tudi o tem, kako ravnati z izzivi, kot so težave z uro, ponastavitev težav in razgradnja signalov.Ne glede na to, ali popravljate napake ali izboljšujete modele, ta vodnik ponuja praktične nasvete in strategije, s pomočjo katerih boste obvladali zaporedna logična vezja.Katalog

Uvod

Zaporedna logična vezja so pomemben vidik digitalnega oblikovanja, ki ga odlikuje njihova sposobnost zadrževanja pomnilnika in izdelave izhodov na podlagi trenutnih vhodov in zgodovinskih stanj.Za razliko od kombiniranih vezij, ki se zanašajo izključno na sedanje vhode, zaporedna vezja vključujejo pomnilniške komponente, ki hranijo pretekla stanja, kar omogoča dinamično in prilagodljivo vedenje.Razmerje med vhodom, pomnilnikom in izhodom je pogosto predstavljeno v blokovnih diagramih, pri čemer se stanje vezja razvija z mehanizmom povratnih informacij, izraženega kot qn+1 = f (x, qn), kjer je x vhod.Zaporedna vezja so razvrščena v zapahe, ki se nenehno odzivajo na vhode, in flip-flops, ki so sinhronizirani s pomočjo urnih signalov.Ta pomnilniška vezja igrajo vlogo v aplikacijah, kot so shranjevanje podatkov in državni stroji, kjer čas in zadrževanje stanja za sistemsko funkcionalnost.Razumevanje prepletanja pomnilnika in logike v teh vezjih je ključno za oblikovanje učinkovitih in naprednih digitalnih sistemov.

Tri logične naprave

Zaporedna logična vezja so odlična za arhitekturo sodobnih digitalnih sistemov, njihova klasifikacija pa je pogosto odvisna od različnih logičnih funkcij.Ta razdelek raziskuje tri ključne naprave, ki zajemajo jedrne atribute zaporednih logičnih vezij, osvetlijo njihove aplikacije in operativne mehanizme.

Števca

V svojem jedru je pult obsegal flip-flops, ki so spretni pri vhodnih impulzih (CP).Izhod števca je sam po sebi vezan na njegovo trenutno stanje, največje število vhodnih impulzov pa se imenuje "modulo", na primer M.medsebojno vplivanje med zmogljivostjo štetja in praktičnimi aplikacijami."Modulo" razmejuje število veljavnih stanj, ki jih lahko števec prikaže za različne uporabe, kot so digitalne ure in frekvenčne delilnike.

Števce je mogoče razvrstiti na podlagi različnih značilnosti, vključno z sistemom štetja (binarni, decimalni, poljubni), smeri štetja (navzgor, navzdol, reverzibilne) in sinhronizacijo (asinhrona v primerjavi s sinhrono).Vsaka razvrstitev izpolnjuje posebno vlogo v digitalnem oblikovanju, s čimer lahko izberete najprimernejšo vrsto za določene aplikacije.Sinhroni števci so v scenarijih za visoke hitrosti pogosto naklonjeni zaradi svojih predvidljivih časovnih atributov, medtem ko lahko asinhroni števci najdejo svoje mesto v enostavnejših modelih, kjer je hitrost manj kritična.

Register

Registri so specializirana vezja, izdelana za oceno številk, rezultatov delovanja ali navodil, ki delujejo kot začasne lokacije za shranjevanje znotraj digitalnih sistemov.Podvrsta, znana kot Shift Registers, omogoča stranski premik shranjenih podatkov kot odgovor na premik impulzov, ki omogoča manipulacijo s podatki in prenos.Prilagodljivost registrov in registrov Shift je komponente v računalnikih in različnih digitalnih napravah.Vsak flip-flop v registru lahko shrani en košček binarnih podatkov, kar omogoča, da N flip-flops skupaj obdrži n bite.

Lastnost flip-flops v registrih je njihova sposobnost, da nastavijo vrednosti na 0 ali 1, ne glede na njihovo konfiguracijo pa naj bo sinhrona, mojstrska suženj ali roba.Ta vsestranskost je potreba po izvajanju kompleksnih operacij, kot so aritmetični izračuni ali pufre podatkov.Zasnova registrov lahko vpliva na delovanje sistema, zlasti glede hitrosti in učinkovitosti, saj pogosto narekujejo hitrost, s katerim je mogoče dostopati do podatkov in obdelavo podatkov.

Zaporedni generator impulzov

Sekvenčni impulzni generator je naprava, ki sčasoma ustvari impulzne signale, razporejene v vnaprej določenem zaporedju.Ti generatorji so odlični v digitalnih sistemih, ki zagotavljajo potrebne časovne signale, ki vodijo naprave pri izvajanju izračunov ali operacij v določenem vrstnem redu.Sposobnost za izdelavo natančnih časovnih signalov se uporablja za sinhronizacijo različnih komponent znotraj sistema, pri čemer zagotavlja, da se operacije odvijajo v pravilnem zaporedju in v ustreznem trenutku.

Na primer, v komunikacijskih sistemih lahko ti generatorji ustvarijo signale ure, ki uravnavajo prenos podatkov.V kontrolnih sistemih orkestrirajo čas mehanskih operacij.Učinkovitost zaporednega generatorja impulzov lahko močno vpliva na splošno delovanje in zanesljivost digitalnega sistema, kar poudarja potrebo po oblikovanju in premišljenem upoštevanju časovnih parametrov.

Lastnosti in izzivi

Zaporedna logična vezja se razlikujejo od kombiniranih vezij, ker njihovi izhodi niso odvisni samo od trenutnih vhodov, ampak tudi od preteklih stanj.Ta sposobnost, da se "zapomnijo", jim omogoča, da obravnavajo funkcije, kot so flip-flops, števci in registri, ki so odlične v aplikacijah, ki segajo od osnovnih časovnikov do naprednih digitalnih sistemov.Zanašanje na zgodovinske vhodne podatke uvaja zapletenost.Na primer, stanje flip-flopa je odvisno od njegovega trenutnega vnosa in prejšnjega stanja, zaradi česar je čas in sinhronizacija.Zamude ali neusklajenosti lahko povzročijo napake.Odpravljanje težav s temi vezji pogosto vključuje simulacije in metode testiranja, kot so opazovanje stanj in manipuliranje vnosov za iskanje neskladij.Zaporedja vhoda-izhod in uporaba simulacijske programske opreme za analizo vedenja vezja skozi čas, kar jim pomaga pri prepoznavanju in reševanju napak.Razumevanje interakcije preteklih in sedanjih vhodov zagotovite, da zanesljivo delujejo zaporedna vezja.

Težave z uro: zagotavljanje zanesljivega časa

Učni signali delujejo kot srčni utrip digitalnih sistemov, kar zagotavlja natančno sinhronizacijo komponent.Napake, kot so izguba signala, premik (frekvenčni premiki) ali tresenje (časovna nihanja), lahko motijo operacije, kar vodi do napak pri prenosu podatkov ali sistemu.Drugi obravnavajo te težave z odpuščanjem (več virov ure) in orodji za spremljanje, ki zaznajo zgodnje znake okvare.Robustno upravljanje ur je dobro za sisteme, ki se zanašajo na natančen čas, kot so telekomunikacije ali avtomobilske aplikacije.Proaktivno upravljanje urnih signalov zagotavlja zanesljivost in uspešnost.

Ponastavitev napak: pomen zanesljivih ponastavitev

Funkcija ponastavitve po napakah obnovi sisteme v znano stanje.Šibki ponastavitve, ki jih povzroča slaba zasnova, nezadostna moč ali motnje, lahko povzročijo nepravilno inicializacijo, kar vodi do zmotnega vedenja ali zrušitve.Drugi okrepijo zanesljivost ponastavitve z dodajanjem vlečnih uporov, zmanjšanjem hrupa s tehnikami razkrivanja in testiranjem pogojev ponastavitve z uporabo simulacij.Učinkoviti mehanizmi za ponastavitev so dobri za stabilnost sistema, ki zagotavljajo nemoteno delovanje in zmanjšanje tveganja za okvaro v aplikacijah.

Napake v avtobusu: vzroki in rešitve

Napake v avtobusu motijo pretok navodil in podatkov, ki pogosto izvirajo iz težav z gonilniki (npr. Zastarela programska oprema) ali napačne strojne opreme (npr. Pomnilnik ali vmesniki).Te napake imajo lahko resne posledice, na primer napačne zdravstvene odmerke ali nepravilnosti finančnega sistema.Preprečevanje napak v avtobusu vključuje redne posodobitve gonilnikov, preglede strojne opreme in uporabo metod preverjanja napak, kot so preverjanje paritete.Te strategije pomagajo ohranjati celovitost podatkov in zanesljivost sistema, zlasti v okoljih, kjer lahko okvare močno vplivajo.

Težave z prekinitvami: upravljanje prekinitev izzivov

Prekini omogočajo mikroprocesorjem, da dajejo prednost nalogam, vendar lahko vprašanja, kot so napačni signali (adhezija vrstice), motnje ali nepravilno ravnanje, motijo izvajanje programa.Za reševanje teh težav je treba s testiranjem zaščititi pred motnjami, tehnikami za odvajanje in rafiniranje protokolov.Dobro zasnovani sistemi predvidevajo prekinitvene težave z uporabo preverjanja napak, odvečnosti in iterativnega izboljšanja.To zagotavlja zanesljive zmogljivosti tudi v zahtevnih pogojih, kar odraža pomen skrbnega oblikovanja in testiranja.

Degradacija signala: ohranjanje celovitosti podatkov

Dolgi vzporedni avtobusi se soočajo s težavami s razgradnjo signala, kot so Crosstalk (motnja med črtami) in hrup iz okoljskih faktorjev ali elektromagnetnih motenj (EMI).Te težave lahko privedejo do podatkovnih napak in napak v sistemu.Številni bojni razgradnjo signala z zaščito, diferencialno signalizacijo in skrbnim dizajnom, kot so razmik žice ali uporaba krajših kablov.Razumevanje in reševanje teh izzivov zagotavlja zanesljivo komunikacijo v elektronskih sistemih, tudi v spreminjajočih se pogojih.

Metoda inšpekcijskega pregleda

Pri popravljanju zaporednih logičnih vezij je pomembno, da najprej razumete arhitekturo in oblikovanje sistema.Podroben pregled napak lahko naredi odpravljanje težav z zmanjševanjem potencialnih vprašanj.V naprednih sistemih, kot so medicinski pripomočki, lahko vgrajena samodiagnostična orodja pomagajo prepoznati težave in prikažejo, kako tehnologija lahko izboljša prakse vzdrževanja.

Preverite napajanje

Zaporedna logična vezja se pogosto zanašajo na napajalnike, kot so ± 5V, ± 15V ali ± 12V.Napake, kot so nestabilne napetosti ali kratki vezji, lahko povzročijo okvare sistema, kot sta neodzivnost ali zmotno vedenje.Napačni kondenzatorji so pogost vzrok kratkih tokokrogov in jih je mogoče zaznati s trenutnim sledilcem.Ohranjanje dnevnika zmogljivosti napajanja lahko pomaga pri napovedovanju težav, preden se pojavijo.

Preverite uro

Urani, izdelani s kremenčevimi kristali ali RC oscilatorji, zagotavljajo natančen čas.Kremenčevi kristali so občutljivi in jih je treba natančno pregledati.Orodja, kot so osciloskopi ali logične sonde, lahko merijo frekvenco, amplitudo in fazo urnega signala, da prepoznajo težave.Vzpostavitev izhodišča za normalno vedenje uro lahko olajša odkrivanje anomalij.

Preverite avtobus

Preverite aktivnost impulza na vodila z logično sondo, da zagotovite pravilno funkcionalnost.Če ni mogoče najti nobene dejavnosti, preglejte gonilnik avtobusa in vhodne signale.Meritve odpornosti lahko pomagajo tudi pri diagnosticiranju težav z avtobusom.Vodenje evidenc o preteklih neuspehih avtobusa lahko zagotavlja koristne vpoglede za prihodnje odpravljanje težav.

Preverite kritične impulzne signale

Kontrolne signale, kot so ponastavitev, omogočanje in branje pomnilnika, je treba spremljati z logičnimi sondami ali osciloskopi.Zdravi signali kažejo, da integrirano vezje (IC) deluje pravilno, medtem ko lahko anomalije kažejo na programske stojnice ali druge težave.Redno dokumentiranje vedenja signala lahko hitreje pomaga diagnosticirati ponavljajoče se težave.

Preverite vmesnik

Ohlapne ali neupravičene povezave lahko povzročijo težave z zmogljivostjo.Čiščenje in varno ponovno povezovanje vmesnikov lahko odpravijo številne napake.Zunanje komunikacijske linije so ranljive za elektromagnetne motnje (EMI), ki lahko motijo prenos podatkov.Zaščita in prepoznavanje virov EMI sta učinkovite preventivne ukrepe.Uporaba kontrolnega seznama za preglede vmesnikov zagotavlja temeljito vzdrževanje.Vzdrževanje zaporednih logičnih vezij zahteva tehnične in lekcije.Uporaba najboljših praks in učenje iz preteklih popravil lahko izboljša zanesljivost in učinkovitost pri odpravljanju težav s temi sistemi.

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Kako EDA preoblikuje delovne tokove Electronics Design?

na 2024/12/31

JPEG je razložil: Osnove, ugodnosti in aplikacije

na 2024/12/31

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/18 147776

-

USB-C pinout in funkcije

na 2000/04/18 112022

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/18 111351

-

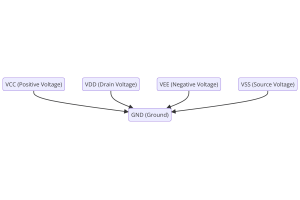

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/18 83777

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79575

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66964

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63104

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63041

-

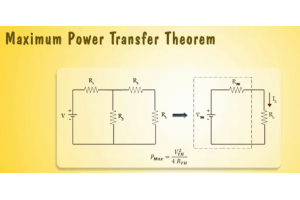

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54097

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52189