XC2S50-5TQG144I FPGA: Funkcije, specifikacije, aplikacije in vodnik za programiranje

XC2S50-5TQG144I je prilagodljiv in zmogljiv FPGA (poljski programirljivi matriki vrat) iz družine Spartan-II AMD Xilinx.Zasnovan je za digitalne projekte, ki potrebujejo prilagoditev, hitrost in zanesljivost.Ta priročnik pojasnjuje funkcije, specifikacije, postopek programiranja in uporabe tega FPGA, da vam pomaga razumeti, kako to kar najbolje izkoristiti.Katalog

Pregled XC2S50-5TQG144I

The XC2S50-5TQG144I je Spartan-II FPGA iz AMD Xilinx, zasnovan za digitalne projekte, ki potrebujejo fleksibilnost in zmogljivost.Ima 50.000 sistemskih vrat in 1.728 logičnih celic, kar mu omogoča, da obravnava zapletene naloge.Čip vključuje 384 nastavljive logične bloke (CLBS) in 32.768 RAM -ov, kar mu daje dober pomnilnik in procesno moč.Z 92 vhodnimi/izhodnimi (V/I) zatiči se lahko enostavno poveže z drugimi komponentami.Na voljo je v 144-polnem tankem štirikolesnem paketu (TQFP), ki je kompakten in enostaven za uporabo.FPGA deluje na 2,5 V (z varnim razponom od 2.375V do 2,625V) in dobro deluje pri temperaturah med -40 ° C in +100 ° C.Ta Spartan-II FPGA je narejen z 0,18-mikron tehnologijo, zaradi česar je učinkovit in zanesljiv.Programira je, kar pomeni, da lahko po potrebi posodobite njegove funkcije.

Za stroškovno učinkovito, visokozmogljivo rešitev je optimalna izbira, ki zagotavlja vrhunsko kakovost.

XC2S50-5TQG144I CAD modeli

Simbol XC2S50-5TQG144I

Odtis XC2S50-5TQG144I

XC2S50-5TQG144I 3D model

Funkcije XC2S50-5TQG144I

• Sistemska vrata: XC2S50-5TQG144I FPGA ponuja približno 50.000 sistemskih vrat.To mu omogoča, da podpira zapletene digitalne zasnove in aplikacije, ki zahtevajo veliko količino logičnih zmogljivosti za obdelavo.

• Logične celice: Ta naprava vključuje 1.728 logičnih celic, ki olajšajo izvajanje zapletenih logičnih konfiguracij in ustvarjajo različne digitalne funkcionalnosti znotraj FPGA.

• Konfiguracijski logični bloki (CLBS): Ima 384 nastavljive logične bloke (CLBS), ki zagotavljajo temelje za logiko FPGA.Te bloke je mogoče programirati in konfigurirati tako, da izpolnjujejo posebne oblikovalske zahteve, kar izboljša celotno vsestranskost naprave.

• Ram: FPGA je opremljena z 32.768 bitov notranjega RAM -a, ki ponuja učinkovite zmogljivosti za shranjevanje in iskanje podatkov za naloge, ki vključujejo manipulacijo s podatki in začasno shranjevanje podatkov.

• I/o zatiči: Z 92 V/I zatiči XC2S50-5TQG144I zagotavlja dovolj zunanje povezave, kar mu omogoča, da se poveže z drugimi napravami in komponentami v sistemu za celovito sistemsko integracijo.

• Delovna napetost: Naprava deluje z nazivno napetostjo 2,5 V, s sprejemljivim območjem od 2.375V do 2,625V.Ta napetostni razpon pomaga zagotoviti stabilno delovanje in zanesljive zmogljivosti v različnih električnih pogojih.

• Temperaturno območje: XC2S50-5TQG144I je zasnovan tako, da učinkovito deluje v širokem temperaturnem območju, od -40 ° C do +100 ° C, zaradi česar je primeren za namestitev v okolju z zahtevnimi toplotnimi pogoji.

XC2S50-5TQG144i blok diagram

Diagram prikazuje, kako se signali premikajo v in iz njega XC2S50-5TQG144I FPGA.Pojasnjuje, kako čip obdeluje vhodne in izhodne signale za komunikacijo z drugimi komponentami.Na izhodna stran , signali prihajajo iz znotraj FPGA in gredo skozi skladiščne enote, imenovane flip-flops.Ti flops vsebujejo podatke in se prepričajo, da se signali spreminjajo ob pravem času.Signali nato preidejo skozi programabilni izhodni medpomnilnik, ki prilagodi, kako močan je signal in nadzoruje, kako hitro se spreminja.Obstaja tudi stikalo (OE Control), ki se odloča, ali naj bo izhod aktiven ali izklopljen.Zaščitno vezje preprečuje poškodbe statične električne energije, preden signal doseže zatiče V/I, ki se povezujejo z drugimi napravami.Na vhodna stran, signali od zunaj vstopijo skozi programirljivi vhodni medpomnilnik, ki jih obdela, preden jih pošlje znotraj FPGA.Programabilna enota za zakasnitev pomaga prilagoditi čas signala, tako da vse ostane v sinhronizaciji.FPGA lahko uporabi tudi notranjo referenčno napetost (VREF), da se ujema z različnimi napetostnimi nivoji, kar olajša delo z različnimi vrstami vezja.Nekateri V/I zatiči delijo to napetostno referenco, da signali ostanejo stabilni.Ta zasnova pomaga FPGA učinkovito upravljati signale, pri čemer zagotavlja pravilno časovno razporeditev, zaščito in združljivost z različnimi elektronskimi komponentami.

Specifikacije XC2S50-5TQG144I

|

Tip |

Parameter |

|

Proizvajalec |

AMD XILINX |

|

Serija |

Spartan®-II |

|

Embalaža |

Pladenj |

|

Status dela |

Zastarelo |

|

Število laboratorijev/CLB |

384 |

|

Število logičnih elementov/celic |

1728 |

|

Skupni ovnovski koščki |

32.768 |

|

Število V/I. |

92 |

|

Število vrat |

50.000 |

|

Napetost - Dobava |

2.375V ~ 2.625V |

|

Vrsta pritrditve |

Površinski nosilec |

|

Delovna temperatura |

-40 ° C ~ 100 ° C (TJ) |

|

Paket / ohišje |

144-LQFP |

|

Paket dobaviteljskih naprav |

144-TQFP (20x20) |

|

Številka osnovnega izdelka |

XC2S50 |

Aplikacije XC2S50-5TQG144I

Vgrajeni sistemi

V vgrajenih sistemih XC2S50-5TQG144I zagotavlja potrebno logiko za aplikacije, ki temeljijo na mikrokontrolerju.Za izboljšanje funkcionalnosti in odzivnosti se široko uporablja v avtomobilski elektroniki, prenosnih napravah in majhnih robotiki.

Obdelava signala

FPGA se odlikuje pri nalogah za obdelavo signalov, kjer je potrebna njegova sposobnost izvajanja vzporedne obdelave.Idealen je za obdelavo zvoka in videov, telekomunikacij in analize podatkov, ki zagotavlja konjske moči za obdelavo kompleksnih algoritmov in hitrih podatkovnih tokov.

Industrijski nadzor

Industrijski krmilni sistemi imajo koristi od robustnosti in programiranosti te FPGA, zaradi česar so primerni za aplikacije, kot so nadzor procesov, avtomatizacija strojev in spremljanje sistema.Njegova zanesljivost zagotavlja dosledno delovanje v okoljih, ki zahtevajo natančnost in operativno stabilnost.

Komunikacijski sistemi

V komunikacijskih sistemih XC2S50-5TQG144I pomaga pri upravljanju prenosa in sprejemanja podatkov, ki podpirajo dejavnosti, kot so signalna modulacija in demodulacija, pretvorba protokolov in usmerjanje omrežja.Njegova prilagodljivost je ključna pri razvijanju telekomunikacijskih infrastruktur in nastajajočih brezžičnih tehnologij.

Prototipizacija in razvoj

FPGA se veliko uporablja tudi za digitalna vezja prototipov.Mnogi ga uporabljajo za testiranje in izpopolnjevanje svojih idej pred končno proizvodnjo, zlasti pri zapletenih projektih ASIC in po meri.Ta sposobnost zmanjšuje razvojni čas in stroške, kar pospeši pot od koncepta na trg.

XC2S50-5TQG144I Podobni deli

Prednosti XC2S50-5TQG144I

Stroškovno učinkovitost

XC2S50-5TQG144I izstopa po ceni, saj zagotavlja več funkcij na dolar kot mnogi konkurenčni FPGA.Ta stroškovno učinkovitost je dosežena z napredno procesno tehnologijo in učinkovito arhitekturo, kar omogoča širšo uvajanje na stroškovno občutljivih trgih.

Visokozmogljiva V/I in embalaža

Ta FPGA podpira široko paleto standardov V/I in je na voljo v različnih stroškovno učinkovitih možnostih embalaže.Te funkcije zagotavljajo, da je mogoče napravo vključiti v več aplikacij, ne da bi pri tem žrtvovali zmogljivosti, zaradi česar je idealna tako za trge višjega cenovnega in volumna, kjer sta vsestranskost vmesnika in fizične omejitve dejavniki.

Funkcije na ravni sistema

Opremljen z naprednimi funkcijami za upravljanje pomnilnika, kot so porazdeljeni RAM in konfigurirani blok RAM, XC2S50-5TQG144i poveča učinkovitost ravnanja s podatki.Te funkcije olajšajo zapletene naloge shranjevanja in obdelave podatkov, kar povečuje celotno delovanje in razširljivost sistema.

Reprogrambilnost

Reprogrambilnost XC2S50-5TQG144i omogoča neomejene spremembe njegove konfiguracije, kar je koristno v fazi razvoja.Ta prilagodljivost omogoča izboljšanje modelov z iterativnimi posodobitvami brez dodatnih stroškov strojne opreme, spodbujanje inovacij in zmanjšanje časa na končni izdelek.

Koraki programiranja XC2S50-5TQG144I

Programiranje XC2S50-5TQG144I FPGA iz serije Spartan-II AMD Xilinx vključuje strukturirano serijo korakov, ki so zasnovani za učinkovito prevajanje digitalne zasnove v funkcionalno konfiguracijo FPGA.Tu je integriran in podroben vodnik, ki vam bo pomagal s pomočjo programiranja:

1. Vnos v oblikovanje

Začnite s fazo vnosa oblikovanja, kjer ustvarite svojo digitalno logiko s pomočjo jezika opisa strojne opreme (HDL), kot sta VHDL ali Verilog.Ta začetni korak vključuje podrobnost funkcionalnosti in logike, ki jo želite izvesti v FPGA.Zahteva se, da je vaša zasnova natančna in natančno predstavlja predvidene operacije za zagotovitev uspešne sinteze in izvajanja.

2. Sinteza

V koraku sinteze uporabite orodje za sintezo za pretvorbo kode HDL v NetList.Netlist je razčlenitev vaše zasnove v obliko, ki vključuje različne medsebojno povezane logične elemente, kot so vrata in flip-flops.Ta postopek prevede vaš teoretični dizajn v praktičen načrt, ki ga FPGA lahko razume in izvaja.

3. Izvedba

Izvedba vključuje več podstopnikov: preslikavo, namestitev in usmerjanje.Kartiranje dodeli elemente vašega seznama Net -a posebnim logičnim blokom znotraj FPGA.Postavitev določa fizične lokacije teh blokov na čipu FPGA za optimizacijo zmogljivosti in uporabe virov.Usmerjanje povezuje te bloke prek programirljivih virov medsebojne povezave FPGA.Ta faza zagotavlja, da zasnova ustreza vsem fizičnim omejitvam in uspešnostjo.

4. Opredelitev omejitve

Med postopkom načrtovanja je potrebna opredelitev omejitev.Omejitve usmerjajo orodja za izvajanje z določitvijo zahtev, kot je čas (kako hitro naj deluje FPGA), in dodelitve PIN (ki se bodo zatiči na FPGA povezali z različnimi deli vaše strojne opreme).Te so artikulirane v datoteki uporabniških omejitev (UCF), ki pomaga pri natančnem nastavitvi zasnove za izpolnjevanje določenih operativnih standardov.

5. Generacija bitstream

Ko vaš dizajn uspešno prehaja skozi fazo izvajanja, je naslednji korak ustvarjanje bitstream datoteke.Ta datoteka vsebuje vse konfiguracijske podatke, ki jih potrebuje FPGA za izvedbo zasnove.Bitstream je končni izhod procesa programiranja, ki predstavlja celotno, programirano stanje FPGA.

6. Programiranje naprav

Končni korak je, da se bitstream naloži v XC2S50-5TQG144I FPGA, ki jo je mogoče izvesti z različnimi načini konfiguracije, odvisno od vaše nastavitve.V Glavni serijski način, FPGA samostojno bere konfiguracijske podatke iz priloženega serijskega maturantskega plesa (programabilni pomnilnik samo za branje). Serijski način suženj Omogoča zunanjo glavno napravo, kot je mikrokontroler, za serijsko napajanje podatkov o konfiguraciji FPGA. Slavni vzporedni način Omogoča programiranje visoke hitrosti z dovajanjem konfiguracijskih podatkov vzporedno z zunanje glavne naprave.Nazadnje, Način mejnega skeniranja (jTAG) Uporablja vmesnik JTAG tako za programiranje kot za testiranje, zaradi česar je uporabna med razvojem za iterativno odpravljanje napak in preverjanje.

Dimenzije embalaže XC2S50-5TQG144I

The XC2S50-5TQG144I je terenski programirljivi vrat (FPGA) iz družine Spartan-II Xilinx, nameščena v a Paket s 144-pinskim tankim štirikotnim paketom (TQFP).Ta paket meri 20 mm x 20 mm.

Proizvajalec XC2S50-5TQG144I

XC2S50-5TQG144I je FPGA iz družine Spartan-II, ki jo je izdelal AMD Xilinx.Xilinx, zdaj del Amd, je vodilno polprevodniško podjetje, specializirano za FPGA, prilagodljive SOC in druge programirljive logične naprave.XC2S50-5TQG144I je bil prvotno razvit v seriji Xilinx Spartan-II, ki ponuja 50.000 sistemskih vrat in 1.728 logičnih celic, zasnovanih za visokozmogljive, a stroškovno učinkovite aplikacije.Z Xilinxovo pridobitvijo AMD podjetje še naprej podpira zapuščene izdelke, kot je serija Spartan-II, medtem ko napreduje novejše arhitekture FPGA.Vendar je XC2S50-5TQG144i starejša generacija FPGA in se lahko sooči z morebitno zastarelostjo, ko se AMD Xilinx preusmeri na bolj napredne družine FPGA.

Zaključek

FPGA XC2S50-5TQG144I je stroškovno učinkovit in reprogramiran čip, ki ponuja odlične zmogljivosti in prilagodljivost.Široko se uporablja v vgrajenih sistemih, industrijskih strojih in komunikacijskih omrežjih zaradi svoje hitre obdelave in močnih možnosti povezljivosti.Ta FPGA s svojo sposobnostjo programiranja in posodobitve pomaga preizkusiti in razviti nove ideje pred končno proizvodnjo.Čeprav so na voljo novejši FPGA, ta model ostaja trdna izbira za projekte, ki potrebujejo zanesljivo in cenovno dostopno rešitev FPGA.Ta priročnik ponuja jasen in preprost pregled funkcij, uporabe in programiranja FPGA, zaradi česar je dragocen vir za vse.

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Pogosto zastavljena vprašanja [FAQ]

1. Ali lahko za aplikacije za visoke hitrosti uporabim XC2S50-5TQG144i?

XC2S50-5TQG144I podpira hitrosti do 200 MHz, zaradi česar je primeren za večino vgrajenih in industrijskih aplikacij.Če pa vaš projekt potrebuje hitre vmesnike, kot sta PCIe ali DDR pomnilnik, boste morda potrebovali bolj napredno FPGA, kot sta serija Spartan-6 ali Artix-7.

2. Kako se XC2S50-5TQG144I primerja z novejšim Spartan-3 ali Spartan-6 FPGA?

Medtem ko novejši FPGA, kot sta Spartan-3 ali Spartan-6, ponujajo izboljšano zmogljivost, večjo logično gostoto in dodatne funkcije, XC2S50-5TQG144i ostaja prednostna izbira za stroškovno občutljive projekte z zmerno zapletenostjo.Če potrebujete zapuščino združljivost ali stabilno dobavno verigo, je odlična možnost XC2S50-5TQG144i.

3. Katera programska orodja so združljiva z XC2S50-5TQG144I FPGA?

XC2S50-5TQG144I je programiran z uporabo Xilinx ISE (integrirano programsko okolje).Medtem ko novejša orodja Xilinx, kot je Vivado, ne podpirajo družine Spartan-II, ISE ponuja vse potrebne zasnove, sinteze in programiranja funkcionalnosti za to FPGA.

4. Ali lahko selim obstoječo zasnovo špartana-II na novejšo FPGA?

Da, vendar zahteva spremembe.Novejše družine Spartan-3 in Spartan-6 uporabljajo različne arhitekture, napetostne ravni in konfiguracijske metode.Če razmišljate o selitvi, vam lahko pomagamo pri izbiri ustreznih alternativ in zmanjšanju sprememb oblikovanja.

5. Ali XC2S50-5TQG144i podpira programiranje JTAG?

O: Da, FPGA podpira JTAG (IEEE 1149.1) Programiranje mejnega skeniranja, ki omogoča enostavno odpravljanje napak in konfiguracijo s standardnim vmesnikom JTAG.To je koristno tako za začetno programiranje kot za konfiguracijo brez zunanjega pomnilnika.

XC4013XL-3PQ240C FPGA: alternative, specifikacije, aplikacije in podatkovni list

na 2025/03/18

RF ojačevalniki moči: kako delujejo, kateri tip je učinkovitejši

na 2025/03/18

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/19 147780

-

USB-C pinout in funkcije

na 2000/04/19 112051

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/19 111352

-

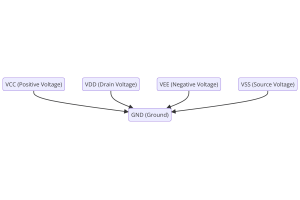

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/19 83806

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79608

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66991

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63113

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63050

-

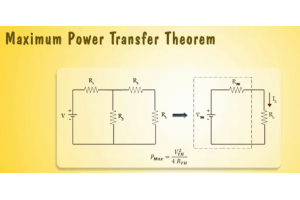

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54097

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52200