EP20K100EFC324-1X FPGA: Funkcije, specifikacije, aplikacije in vodnik za programiranje

EP20K100EFC324-1X je programirljiv čip (FPGA) iz Intelove serije Altera Apex-20ke®.Zasnovan je za ravnanje z zapletenimi digitalnimi vezji in podpira obdelavo podatkov z visoko hitrostjo.Ta priročnik pojasnjuje svoje lastnosti, specifikacije, kako ga programirati in njene prednosti, s čimer je koristen vir za vse.Katalog

Pregled EP20K100EFC324-1X

The EP20K100EFC324-1X je del Intelove serije Altera Apex-20ke®, poljskega programirljivega matrika vrat (FPGA), prilagojenega za programirne logične aplikacije z visoko gostoto, ki zahtevajo prefinjene integracije sistema na programiranem čipu (SOPC).To napravo odlikuje njena integracija 4.160 logičnih elementov ali celic in 416 logičnih blokov (laboratorij), ki olajšajo bistveno konfiguracijo za različne digitalne modele vezja.Prav tako se ponaša z veliko količino vgrajenega pomnilnika, ki ustreza zahtevnim zahtevam za shranjevanje podatkov znotraj FPGA.EP20K100EFC324-1X podpira 246 V/I zatičev in ponuja znatno število vrat in ponuja približno 263.000 enakovrednih vrat, ki učinkovito delujejo med 1,71 V do 1,89 V.Pakiran je v kroglični matriki z drobno žogo s 324 kroglicami (FBGA), ki pomaga pri močni fizični integraciji v elektronske sklope.

EP20K100EFC324-1X je odlična izbira, ko ste pripravljeni na oddajanje naročil za svoje projekte ali linije izdelkov.

EP20K100EFC324-1X CAD modeli

Simbol EP20K100EFC324-1X

Odtis EP20K100EFC324-1X

EP20K100EFC324-1X 3D model

Funkcije EP20K100EFC324-1X

• Visoka logična gostota: FPGA je opremljena s 4.160 logičnimi elementi (LES) in 416 logičnimi matričnimi bloki (laboratoriji).Ta visoka gostota logičnih celic omogoča oblikovanje in izvajanje zapletenih digitalnih vezij in sistemov znotraj enega čipa, zaradi česar je idealen za aplikacije, ki zahtevajo robustne zmogljivosti za obdelavo logike.

• Vgrajen pomnilnik: Ponuja 53.248 RAM -ov, ta FPGA ponuja velike vgrajene pomnilniške vire.Ta funkcija je dobra za aplikacije, ki zahtevajo hitro shranjevanje in iskanje podatkov, kar omogoča učinkovito ravnanje z podatkovnimi nalogami.

• Obsežne zmogljivosti I/O.: S 246 vhodnimi/izhodnimi zatiči EP20K100EFC324-1X zagotavlja celovite možnosti povezljivosti in povezovanja.Ta širok razpon zmogljivosti V/I mu omogoča enostavno povezovanje z množico zunanjih naprav in sistemov, kar izboljšuje njegovo uporabnost v zapletenih elektronskih sklopih.

• Več-napetost podpora: Naprava podpira območje jedrne napetosti od 1,71V do 1,89V in ima Multivolt ™ V/I povezovanje.To omogoča, da je FPGA združljiv z drugimi elektronskimi komponentami, ki delujejo na različnih logičnih nivojih, vključno z 1,8 V, 2,5V, 3,3V in 5,0V, kar zagotavlja veliko prilagodljivost pri zasnovi sistema.

EP20K100EFC324-1X blok diagram

The EP20K100EFC324-1X blok diagram Predstavlja notranjo strukturo naprave FPGA (polja programirljivo matriko vrat), ki prikazuje svoje različne funkcionalne enote.Diagram je sestavljen iz medsebojno povezanih logičnih blokov, pomnilniških elementov, upravljanja ur in V/I elementov.V jedru zasnove so Bloki logične matrike (Labs), ki vsebujejo Iskalne mize (LUTS) in logika, ki temelji na izdelku.Ti elementi omogočajo fleksibilno logično izvajanje, zaradi česar je FPGA primeren za visokohitrostne kontrolne logike, državne stroje in funkcije DSP.The Hitri medkonnect Omogoča hitro komunikacijsko pot med logičnimi elementi, ki zagotavlja učinkovito usmerjanje signala po vsej napravi.The Vezje za upravljanje ur , vključno s funkcijo Clocklock, zagotavlja zanesljivo in sinhronizirano delovanje s stabilizacijo in distribucijo urnih signalov po FPGA.The Vhodni/izhodni elementi (IOES), nameščeni okoli tkanine FPGA, služijo kot vmesniki za zunanjo komunikacijo.Ti IOE podpirajo več industrijskih standardnih protokolov, kot so PCI, GTL+, SSTL-3in LVD -ji, ki omogoča FPGA, da se poveže z različnimi zunanjimi sistemi.Ti IOE zagotavljajo združljivost z različnimi napetostnimi stopnjami in signalnimi standardi, kar izboljšuje vsestranskost FPGA v vgrajene aplikacije. Vgrajeni pomnilniški bloki Zagotovite prilagodljive rešitve za shranjevanje znotraj FPGA.Ti pomnilniški elementi lahko delujejo kot Vsebina naslovni pomnilnik (Cam), Pomnilnik naključnega dostopa (RAM), Pomnilnik samo za branje (ROM), Prvo v prvem mestu (FIFO) medpomnilniki in druge pomnilniške strukture.Sposobnost integracije pomnilnika neposredno znotraj tkanine FPGA izboljšuje učinkovitost obdelave podatkov, kar zmanjša zunanje odvisnosti pomnilnika in zamude.

Specifikacije EP20K100EFC324-1X

|

Tip |

Parameter |

|

Proizvajalec |

Intel |

|

Serija |

Apex-20ke® |

|

Embalaža |

Pladenj |

|

Status dela |

Zastarelo |

|

Število laboratorijev/CLB |

416 |

|

Število logičnih elementov/celic |

4160 |

|

Skupni ovnovski koščki |

53248 |

|

Število V/I. |

246 |

|

Število vrat |

263000 |

|

Napetost - Dobava |

1.71V ~ 1.89V |

|

Vrsta pritrditve |

Površinski nosilec |

|

Delovna temperatura |

0 ° C ~ 85 ° C (TJ) |

|

Paket / ohišje |

324-BGA |

|

Paket dobaviteljskih naprav |

324-FBGA (19x19) |

|

Številka osnovnega izdelka |

EP20K100 |

Aplikacije EP20K100EFC324-1X

Mreženje in komunikacije

Ta FPGA je idealna za omrežno opremo, kot so usmerjevalniki in stikala, kjer upravlja usmerjanje podatkov, obdelavo signalov in ravnanje z protokolom.Njegova visoka logična gostota in obsežne zmogljivosti V/I omogočajo podpiranje zapletenih podatkovnih operacij visokih hitrosti, potrebnih v sodobni komunikacijski infrastrukturi.

Industrijski nadzor

V industrijskem sektorju EP20K100EFC324-1X odlikuje v sistemih za avtomatizacijo.Njegova programiranost in močne zmogljivosti obdelave omogočajo natančen nadzor in spremljanje za izboljšanje operativne učinkovitosti in zanesljivosti v proizvodnih procesih.

Avtomobilska elektronika

FPGA služi kot sestavni del avtomobilskih aplikacij, zlasti v naprednih sistemih za pomoč vozniku (ADAS) in v sistemih za zabavo v vozilih.Zagotavlja potrebno procesno moč in prilagodljivost za ravnanje z podatki in podpiranje prefinjenih funkcionalnosti, potrebnih v sodobnih vozilih.

Potrošniška elektronika

Zaradi svoje prilagodljivosti in visoke zmogljivosti najdemo tudi EP20K100EFC324-1X tudi v potrošniški elektroniki, kot so televizorji z visoko ločljivostjo in igralne konzole.Podpira zapletene funkcionalnosti in pomaga pri skrajšanju ciklov razvoja izdelkov, pri čemer izpolnjuje hitro povpraševanje na trgu potrošniške elektronike.

Medicinske pripomočke

Na medicinskem področju ta FPGA prispeva k funkcionalnosti opreme za slikanje in diagnostičnim orodjem.Njegova sposobnost obdelave podatkov pri visokih hitrostih zagotavlja, da lahko te naprave dosežejo natančne in pravočasne diagnostične rezultate za učinkovito zdravstveno zdravljenje in slikanje.

EP20K100EFC324-1X podobni deli

Koraki programiranja EP20K100EFC324-1X

Če želite učinkovito programirati EP20K100EFC324-1X, člana serije FPGA APEX-20KE® APEX-20KE®, je pomembno slediti strukturiranemu zaporedju korakov.Ta postopek zagotavlja, da je vaš dizajn učinkovito preveden v obliko, ki jo lahko izvede FPGA.Spodaj opisujem podroben pristop k programiranju tega modela FPGA, ki vključujejo korake in spremembe, značilne za to napravo.

1. Vnos v oblikovanje

Začnite z ustvarjanjem digitalne logične zasnove.Uporabite opis strojne opreme (HDL), kot sta VHDL ali Verilog, ki omogočajo opis funkcije strojne opreme in logiko vašega sistema.Orodja, kot je Altera's Quartus II, ponujajo celovito okolje za pisanje, testiranje in sestavljanje kode HDL.Prepričajte se, da je vaš dizajn modularen, kar olajša odpravljanje napak in obsega.

2. Sinteza

Ko je vnos oblikovanja končan, je naslednji korak sinteza, kjer je koda HDL prevedena na mrežni seznam.Ta mrežni seznam predstavlja medsebojno povezan seznam vrat, flip-flops in drugih strojnih elementov, ki sestavljajo vaš dizajn.Med sintezo je koda optimizirana za specifično arhitekturo EP20K100EFC324-1X, s čimer zagotavlja, da zasnova učinkovito uporablja vire FPGA.V ta namen se lahko uporabijo orodja, kot sta Synplify Pro ali Sintezo v Quartus II.Pomembno je, da se osredotočite na optimizacijo svojega dizajna, da dosežete omejitve časa in virov.

3. Izvedba

Po sintezi poteka izvedba.Ta korak vključuje preslikavo seznama Net na dejansko strojno opremo FPGA.Vključuje namestitev logičnih elementov znotraj FPGA in usmerjanje povezav med njimi.Programska oprema Quartus II ta postopek olajša s svojimi orodji za izvajanje, ki upravljajo s umestitvijo in usmerjanjem, da dosežejo želene hitrosti ure in meritve uspešnosti.Med izvajanjem boste morda morali ponoviti svojo zasnovo na podlagi povratnih informacij iz orodij za analizo časovne analize, da zagotovite izpolnjene vse zahteve glede zmogljivosti.

4. Generacija bitstream

Po uspešni izvedbi je naslednja faza ustvarjanje bitstreama.To je binarna datoteka, ki bo naložena na FPGA.Bitstream vsebuje konfigurirane podatke za vsak programabilni element v FPGA in nastavi napravo za izvajanje funkcij po vašem dizajnu.Programska oprema Quartus II lahko ustvari ta bitstream, ki je nato pripravljen za prenos na FPGA.

5. Programiranje FPGA

Končni korak je programiranje FPGA z ustvarjenim bitstream -om.To je mogoče storiti z uporabo strojnega programerja, združljivega z EP20K100EFC324-1X, kot je USB Blaster.Priključite programerja s svojo razvojno ploščo, kjer je nameščen FPGA, in uporabite orodje za programerja Quartus II za prenos bitstreama na FPGA.Ta korak bo vaš dizajn naložil na FPGA in začel bo delovati v skladu z logiko, določeno v vaši kodi HDL.

Prednosti EP20K100EFC324-1X

Visoka integracija

EP20K100EFC324-1X ponuja visoke zmogljivosti integracije zaradi velikega števila logičnih elementov in vgrajenega pomnilnika.Ta integracija omogoča konsolidacijo več funkcionalnosti v eno napravo.Kot rezultat, lahko sisteme poenostavimo, kar zmanjša celotno število komponent, potreben fizični prostor in potencialne točke okvare v elektronskih modelih.

Prilagodljiva logična izvedba

Arhitektura EP20K100EFC324-1X podpira tako iskalno tabelo (LUT) kot logiko, ki temelji na izdelku.Ta prilagodljivost pri logični implementaciji omogoča optimizacijo FPGA za široko paleto aplikacij, od preprostih logičnih vrat do kompleksnih kombiniranih vezij.Ponuja prednost v smislu vsestranskosti oblikovanja in lahko sprejme širok spekter digitalnih funkcionalnosti.

Napredna struktura medsebojne povezave

FPGA, ki vsebuje hierarhično strukturo medsebojne povezave, vključuje medsebojne povezave Local, Megalab ™ in Fasttrack®.Ti specializirani viri usmerjanja povečujejo učinkovitost usmerjanja signala in izboljšajo splošno delovanje naprave.Ta napredna struktura medsebojnega povezovanja je dobra za modele, ki zahtevajo hitro prenos podatkov in nizke zamude, zaradi česar je FPGA idealen za visokozmogljivo računalništvo in telekomunikacije.

Upravljanje ur

EP20K100EFC324-1X vključuje tehnologijo Clocklock in Clockboost, ki pomaga pri učinkovitem upravljanju ure.Te lastnosti pomagajo pri ohranjanju celovitosti signala ure v celotni FPGA, zmanjšanju tresenja in izboljšanju zanesljivosti signala.Učinkovito upravljanje ur je potrebno za sinhrona digitalna vezja, ki zagotavljajo stabilno in predvidljivo delovanje v različnih okoljskih pogojih.

Prožnost oblikovanja

Programabilna narava EP20K100EFC324-1X omogoča prilagoditev strojne opreme specifičnim potrebam in ponovno konfigurira FPGA za različne aplikacije ali posodobitve.Ta prilagodljivost pomeni, da se lahko en FPGA uporablja v več projektih, kar je koristno v dinamični tehnološki pokrajini, kjer se zahteve lahko hitro spremenijo.

Hitro prototipizacijo

FPGA, kot je EP20K100EFC324-1X, omogočajo hitro prototipiranje digitalnih vezij.Hitro lahko razvijete in ponavljate modele brez dolgih časov svinca, povezanih z razvojem ASIC po meri.Ta sposobnost hitrega modeliranja in testiranja novih modelov pospešuje razvojni proces, kar vodi do hitrejših inovacij in skrajša čas na trgu.

Stroškovno učinkovitost

Vključevanje več funkcij v enem samem FPGA zmanjšuje potrebo po dodatnih diskretnih komponentah, kar lahko privede do prihrankov stroškov tako pri javnih naročilih kot pri montaži.Ta integracija tudi poenostavi proizvodni postopek in lahko zmanjša celotno kompleksnost sistema, kar vodi do nižjih stroškov vzdrževanja in nadgradnje v življenjskem ciklu izdelka.

Dolgoročna podpora

Ponovni konfiguracijski vidik EP20K100EFC324-1X zagotavlja, da je mogoče posodobiti strojno opremo za popravljanje napak, izboljšanje zmogljivosti ali dodajanje novih funkcij, ne da bi bilo potrebno fizične spremembe strojne opreme.Ta dolgoročna podpora in prilagodljivost ščitita naložbe in omogočajo, da ostanejo pomembni, ko se pojavljajo novi standardi in tehnologije.

EP20K100EFC324-1X dimenzije embalaže

EP20K100EFC324-1X je FPGA iz serije Altera Apex-20ke®, nameščena v a 324-kroglični kroglični omrežji (FBGA) paket.Njegove dimenzije embalaže so naslednje:

• Nagib: 1 mm

• Dolžina × širina: 19 mm × 19 mm

• Območje: 361 mm²

Proizvajalec EP20K100EFC324-1X

EP20K100EFC324-1X je model iz serije APEX-20KE® serije programirljivih vrat polja (FPGA), ki ga je prvotno razvila Altera.Po Intelovem pridobitvi Altera leta 2015 so ta FPGA in drugi izdelki Altera postali del Intelovega obsežnega programirljivega portfelja rešitev.Kot rezultat, Intel Še naprej podpira Alterove linije izdelkov, hkrati pa jih integrira z lastno napredno tehnološko ponudbo.Čeprav je bil EP20K100EFC324-1X razvrščen kot zastarel in ni več v proizvodnji, se njegova zapuščina vzdržuje pod Intel, kar priporoča novejše modele FPGA za trenutne aplikacije, da se zagotovi dolgoročna podpora in razpoložljivost.

Zaključek

EP20K100EFC324-1X je zmogljiv in prilagodljiv FPGA, ki omogoča ustvarjanje in testiranje digitalnih vezij po meri.Ponuja visoko zmogljivo, vgrajen pomnilnik in večkratno podporo, zaradi česar je uporabna v mnogih panogah.Ta vodnik vas je popeljal skozi glavne funkcije, oblikovanje in korake za programiranje tega FPGA na preprost način, tako da ga lahko enostavno razumete in uporabljate.

PDF podatkovnega lista

EP20K100EFC324-1X podatkovne liste:

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Pogosto zastavljena vprašanja [FAQ]

1. Kako se EP20K100EFC324-1X primerja z novejšimi modeli FPGA?

EP20K100EFC324-1X ostaja močan FPGA za zapuščene sisteme in industrijske aplikacije, ki zahtevajo visoko logično gostoto in prilagodljive zmogljivosti V/I.Vendar pa v primerjavi s sodobnimi FPGA, kot so Intelova serija Cyclone, Arria ali Stratix, nima napredne učinkovitosti moči, oddajnikov za visoke hitrosti in pospeševanju, ki ga poganja AI.Če oblikujete nov sistem, lahko predlagamo enakovredne ali nadgrajene modele.

2. Ali EP20K100EFC324-1X podpira zunanje pomnilniške vmesnike, kot sta DDR ali SRAM?

Da, EP20K100EFC324-1X podpira zunanje pomnilniške vmesnike, vključno s SRAM in SDRAM.Vendar pa ne podpira DDR2/DDR3.Če je potrebno povezovanje pomnilnika visoke hitrosti, bo morda potrebna dodatna zunanja logika ali novejša FPGA.

3. Ali lahko večkrat ponovno konfiguriram EP20K100EFC324-1X?

Da, tako kot vsi FPGA je tudi ta naprava v celoti reprogramiranljiva.Če pa uporabite nestabilno konfiguracijo, boste potrebovali zunanji pomnilnik (na primer serijski maturant), da ohranite zasnovo po kolesarjenju z napajanjem.

4. Ali lahko programiram EP20K100EFC324-1X z uporabo programske opreme Intel Quartus?

Da, lahko programirate EP20K100EFC324-1X z uporabo Intel Quartus II (zapuščene različice), saj ta FPGA pripada družini Apex-20ke®.Prepričajte se, da vaša različica Quartus II podpira to napravo, saj novejše izdaje Quartus Prime ne podpirajo zapuščenih FPGA.

5. Katere zahteve za napajanje naj upoštevam pri uporabi EP20K100EFC324-1X?

EP20K100EFC324-1X deluje z območjem jedrne napetosti od 1,71V do 1,89V.Vsebuje tudi tehnologijo Multivolt ™ V/I, ki podpira nivo 1,8V, 2,5V, 3.3V in 5,0V.Prepričajte se, da je vaš napajalnik izpolnjevanje teh napetostnih zahtev za stabilne zmogljivosti.

XCV200-6FG456C FPGA: Funkcije, specifikacije, programiranje in aplikacije

na 2025/03/20

Zakaj so 0603 komponente priljubljene v sodobni elektroniki

na 2025/03/20

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/18 147780

-

USB-C pinout in funkcije

na 2000/04/18 112050

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/18 111352

-

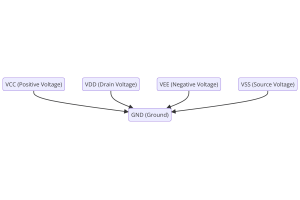

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/18 83806

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79608

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66988

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63113

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63049

-

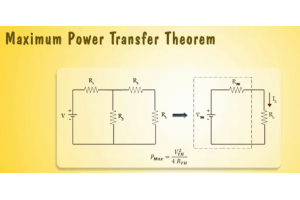

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54097

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52199