XCV200-6FG456C FPGA: Funkcije, specifikacije, programiranje in aplikacije

XCV200-6FG456C je zmogljiva FPGA (poljsko vgradljivo matriko vrat) iz serije AMD Xilinx Virtex®.Ta vodnik pojasnjuje svoje lastnosti, postavitev pin, korake programiranja in uporabe.Z visoko procesno močjo, prilagodljivimi možnostmi oblikovanja in močnimi vhodnimi/izhodnimi (V/I) zmožnostmi, ta FPGA pomaga graditi hitre in zanesljive digitalne sisteme.Ne glede na to, ali delate na omrežjih, nadzornih sistemih ali elektroniki po meri, vam bo ta priročnik pomagal razumeti, kako lahko v vaših projektih uporabite XCV200-6FG456C.Katalog

Pregled XCV200-6FG456C

The XCV200-6FG456C je pomemben model v družini AMD Xilinx VirX® FPGA, zasnovan za zagotavljanje robustnih programirljivih logičnih rešitev za zapletene digitalne sisteme.Ta specifični čip obsega približno 236.666 sistemskih vrat in ima 1,176 nastavljive logične bloke (CLB) in 5.292 logičnih celic.Vključuje tudi 57.344 Skupnih Ram-jevih koščkov in podpira 284 I/O zatičev, nameščenih v paketu krogličnega omrežja s fino-kroglicami s 456 kroglicami (FBGA), ki meri 23 mm x 23 mm.Ta model deluje na 2,5V nazivni napetosti, z razponom od 2.375V do 2,625V in lahko deluje v temperaturnem območju od 0 ° C do 85 ° C.Širša serija VirX® skrbi za vrsto aplikacij z gostoto od 50.000 do več kot milijon sistemskih vrat in sistemskih stopenj do 200 MHz.Med drugim podpira številne standarde V/I, vključno z LVTTL, LVCMO in PCI.Značilnosti, kot so zanke z zamudo (DLL), nastavljivi logični bloki z vgrajenim pomnilnikom in namenska logika nosilca za aritmetične operacije, izboljšujejo njegovo funkcionalnost.Izdelana s pomočjo 5-slojnega kovinskega procesa 0,22 µm, družina VirX® zagotavlja zmogljivost in zanesljivost.

Če želite v svoje izdelke ali sisteme vključiti najvišje tehnologijo FPGA, je nakup XCV200-6FG456C v razsutem stanju pri nas pametna poteza.Ustreza industrijskim standardom in vas ohranja pred prihodnjimi tehnološkimi potrebami.

Funkcije XCV200-6FG456C

• Sistemska vrata: XCV200-6FG456C ponuja približno 236.666 sistemskih vrat.To visoko število vrat omogoča izvajanje kompleksnih integriranih digitalnih logičnih vezij na enem samem čipu, kar izboljšuje tako zmogljivost kot vsestranskost v različnih aplikacijah.

• Logični viri: Vključuje 1,176 nastavljive logične bloke (CLB) in 5.292 logičnih celic.Ti viri so dobri za oblikovanje prilagodljivih in razširljivih digitalnih vezij.CLB lahko programiramo tako, da izvajajo najrazličnejše logične funkcije, medtem ko veliko število logičnih celic omogoča ravnanje z obsežnimi logičnimi operacijami in procesi.

• Spomin: Naprava ponuja 57.344 bitov RAM -a, razporejene med njenimi logičnimi bloki.Ta vgrajeni RAM se uporablja za aplikacije, ki zahtevajo hitro in učinkovito shranjevanje in iskanje podatkov, kar podpira hitre podatkovne operacije, ki so sestavni del sodobnih digitalnih sistemov.

• I/O zmogljivosti: Z 284 vhodnimi/izhodnimi zatiči XCV200-6FG456C olajša obsežne zmogljivosti za povezovanje.Ti zatiči V/I podpirajo različne signalne standarde in omogočajo učinkovito komunikacijo FPGA z drugimi komponentami v sistemu, kot so pomnilniške naprave, procesorji in periferne naprave.

• Napetostno in temperaturno območje: Deluje z nazivno napetostjo 2,5 V, s sprejemljivim območjem od 2.375V do 2,625V, ta FPGA je zasnovana za porabo z majhno močjo, hkrati pa ohranja močne zmogljivosti.Deluje lahko v temperaturnem območju stika od 0 ° C do 85 ° C, kar zagotavlja zanesljivost v različnih okoljskih pogojih.

XCV200-6FG456C PIN FUNKCIJS

The XCV200-6FG456C PIN FUNKCIJS je strukturirana predstavitev dodelitev PIN FPGA, razvrščena v različne banke (Bank 0 to Bank 7).Vsaka bančna skupina se zatakne na podlagi njihove funkcije in fizične namestitve na paketu FPGA.The numbering and labeling system follows a grid pattern where rows are denoted by letters (A, B, C, etc.), and columns by numbers (1, 2, 3, etc.), which facilitates quick identification of specific pins.Te banke ustrezajo različnim vhodnim/izhodnim funkcijam, moči, ozemljitvi in namenskim usmerjanjem signala.Pins are assigned various functional groupings, including General-Purpose I/O (GPIO), often labeled as "G" (General Input/Output), "V" (Voltage supply), and "O" (Output).Moč in zemeljski zatiči so izrazito označeni, kar zagotavlja stabilno delovanje FPGA.Zatiči posebne namene, kot so vhodi ure, ponastavitve in krmilni signali, se identificirajo s simboli, kot sta "R" ali "T."Nekateri zatiči služijo tudi namenskim komunikacijskim vlogam, vključno s konfiguracijo JTAG in visoko hitrostjo, za programiranje in odpravljanje napak.

XCV200-6FG456C blok diagram

Vhodni/izhodni blok

Diagram predstavlja Vhodni/izhodni blok (IOB) Struktura XCV200-6FG456C FPGA, ki je član družine Xilinx Virtex.Diagram prikazuje ključne elemente, ki so vključeni v vhodne in izhodne operacije, ki poudarjajo mehanizme pretoka in krmiljenja podatkov.V jedru diagrama se za registracijo signalov za vhod, izhod in tridržavno krmiljenje uporabljajo trije d.Izhodni register nadzoruje signal OCE (izhodna ura), ki določa, kdaj so izhodni podatki zaskočeni.Podobno je register Tri-State nadzorovan s TCE (Tri-State Clock Enable), ki omogoča ali onemogoči izhodni medpomnilnik.The input register captures incoming data and applies a programmable delay before passing it to the internal FPGA logic through the IBUF (Input Buffer).The OBUFT (Tri-State Output Buffer) ensures that the FPGA can either drive a signal onto the PAD (I/O pin) or place it in a high-impedance state, depending on the control logic.A weak keeper circuit is included on the PAD to maintain the last known logic state when no active driver is present, preventing unintended floating conditions.The reference voltage (Vref) is used for certain input standards, such as SSTL or HSTL, which require precise voltage levels for proper operation.Overall, this IOB structure allows the FPGA to manage high-speed data transmission, support different I/O standards, and provide flexible control over signal timing and integrity.

Glavni/podrejeni serijski način

The Glavni/podrejeni serijski način block diagram illustrates the configuration process of a Virtex FPGA, specifically the XCV200-6FG456C, when programmed in a daisy-chain configuration using a serial EEPROM (XC1701L).In this setup, one Virtex device operates as the Master, controlling the configuration clock (CCLK) and serially transmitting configuration data to additional Slave FPGAs in the chain.Glavni FPGA sproži postopek konfiguracije tako, da uveljavlja programski signal in ponastavi vse naprave v verigi.Once initialization is complete, the INIT signal indicates readiness, and configuration data flows from the serial EEPROM (XC1701L) to the DIN (Data In) pin of the Master FPGA.The Master FPGA reads data from the EEPROM and forwards it through DOUT (Data Out) to subsequent Slave FPGAs, synchronizing data transfer using the CCLK signal.The DONE signal is used to indicate successful configuration, with an optional pull-up resistor ensuring a stable high state when configuration is complete.The XC1701L EEPROM is controlled by the Master FPGA using CLK, DATA, CE (Chip Enable), and RESET/OE (Output Enable) signals, ensuring that the stored configuration data is correctly retrieved.This configuration method is efficient for programming multiple FPGAs using a single EEPROM, reducing external wiring complexity and ensuring all devices receive synchronized configuration data.

Specifikacije XCV200-6FG456C

|

Tip |

Parameter |

|

Proizvajalec |

AMD XILINX

|

|

Serija |

Virtex® |

|

Embalaža |

Pladenj |

|

Status dela |

Zastarelo |

|

Število laboratorijev/CLB |

1176 |

|

Število logičnih elementov/celic |

5292 |

|

Skupni ovnovski koščki |

57344 |

|

Število V/I. |

284 |

|

Število vrat |

236666 |

|

Napetost - Dobava |

2.375V ~ 2.625V |

|

Vrsta pritrditve |

Površinski nosilec |

|

Delovna temperatura |

0 ° C ~ 85 ° C (TJ) |

|

Paket / ohišje |

456-BBGA |

|

Paket dobaviteljskih naprav |

456-FBGA (23x23) |

|

Številka osnovnega izdelka |

XCV200 |

XCV200-6FG456C aplikacije

Telekomunikacije in mreženje

The XCV200-6FG456C excels in telecommunications and networking applications due to its ability to handle high-speed data transmissions and complex signal processing tasks.Its high gate count and robust I/O capabilities allow it to support functions such as packet processing, signal modulation/demodulation, and error correction protocols.

Digitalna obdelava signalov (DSP)

Ideal for DSP applications, this FPGA can perform rapid and complex mathematical computations required in audio and video processing technologies.Whether it's for multimedia systems, voice recognition, or streaming services, the XCV200-6FG456C's powerful processing capabilities and embedded memory support efficient and high-quality signal processing.

Industrijski nadzor

V industrijski avtomatizaciji XCV200-6FG456C zagotavlja potrebno zmogljivost za upravljanje nadzornih sistemov in omrežij za avtomatizacijo.Its ability to execute multiple control tasks simultaneously while ensuring response times makes it suitable for applications in process control, robotics, and machine vision.

Medicinski instrumenti

The FPGA's precision and speed are great in medical imaging and diagnostic equipment, where it aids in the processing of complex algorithms for imaging applications such as MRI, ultrasound, and CT scans.Zmogljivosti XCV200-6FG456C zagotavljajo, da lahko obvladuje visoko pretok podatkov in zapleteno obdelavo, ki je potrebna v sodobni medicinski tehnologiji.

XCV200-6FG456C Podobni deli

XCV200-6FG456C Programming Steps

Korak programiranja za XCV200-6FG456C:

1. Vnos v oblikovanje

Začetna faza programiranja FPGA vključuje določitev digitalne logike in funkcionalnosti vašega sistema.This can be done using Hardware Description Languages (HDLs) such as VHDL or Verilog, where you write code that specifies how the FPGA processes data and interacts with other hardware.Shematična orodja za vnos, ki so na voljo v programski opremi FPGA, sta lahko uporabili Xilinx ISE ali Vivado.This method involves creating a visual representation of the logic by dragging and dropping components, which some find more intuitive than writing code.

2. Sinteza

Once the design is completed, the next step is synthesis, where a tool like Xilinx's XST (Xilinx Synthesis Technology) transforms your HDL code or schematic design into a netlist.Ta mrežni seznam opisuje vezje glede na generične digitalne komponente, kot so logična vrata in registri.The synthesis process also involves optimizing the design to meet performance requirements and minimize resource usage for efficient FPGA operation.

3. Izvedba

The implementation process begins with translation, combining your design with constraint files that specify parameters such as clock frequencies and pin assignments.Following translation, the mapping stage assigns the elements of your netlist to specific physical resources on the FPGA, like Look-Up Tables (LUTs) and flip-flops.The placement and routing phase then determines the physical locations of each component within the FPGA's architecture and establishes the connections between them through programmable interconnect resources.Ta faza je odlična za doseganje želenih meritev uspešnosti, vključno s frekvencami ure.

4. Generacija bitstream

After successful placement and routing, the tool generates a bitstream, a binary configuration file that contains all the programming information for the FPGA.Pogosto je priporočljivo simulirati končno zasnovo po postavitvi, da se zagotovi, da se bo bitstream obnašal, kot je bilo pričakovano pod pogoji.Ta korak preverjanja pomaga, da se med dejanskim delovanjem izognemo morebitnim težavam.

5. Konfiguracija

Končni korak vključuje nalaganje bitstreama v FPGA z uporabo različnih konfiguracijskih metod.Način sužnjev serial, preprosta in stroškovno učinkovita možnost, konfigurira FPGA prek zunanje glavne naprave, ki podatke serijsko pošilja.V načinu Master-Serial FPGA avtonomno bere bitstream iz priloženega serijskega maturantskega plesa.Za konfiguracije za visoke hitrosti način SelectMap omogoča zunanjim mikroprocesorjem, da hitro naloži podatke v FPGA.Additionally, JTAG mode is used not only for programming but also for testing and debugging, utilizing a standard interface for in-system programming and boundary-scan testing.

XCV200-6FG456C PREDNOSTI

Uspešnost

The Xilinx Virtex series, to which the XCV200-6FG456C belongs, is optimized for high-speed performance, offering system clock rates of up to 200 MHz.This makes it well-suited for applications that require fast data processing, ensuring efficient handling of complex algorithms and high-speed operations like telecommunications, processing, and multimedia.

V/I Standardi Podpora

Ta FPGA podpira široko paleto vhodnih/izhodnih standardov, vključno z LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT in AGP.Such extensive I/O standards support enables the XCV200-6FG456C to integrate seamlessly with various system components, enhancing its utility across diverse digital ecosystems.Ta prilagodljivost omogoča prilagoditev FPGA na različne pogoje vmešavanja brez sistema.

Upravljanje ur

XCV200-6FG456C vključuje več zadolženih zanke (DLL-jev) za porazdelitev in upravljanje ure znotraj sistema.Ti DLL -ji pomagajo pri izboljšanju sistema in zanesljivosti z zagotavljanjem natančnih urnih signalov, potrebnih za sinhrone operacije.This feature is important in reducing system errors and enhancing overall performance, particularly in complex designs requiring accurate timing and synchronization.

Prožnost oblikovanja

With 1,176 Configurable Logic Blocks and 5,292 logic cells, the XCV200-6FG456C offers substantial logic resources with the capability to implement a diverse range of functionalities.From simple glue logic to intricate digital systems, this FPGA supports complex design requirements, making it ideal for applications in custom computing, digital signal processing, and prototyping.

Hitro prototipizacijo

FPGA, kot je XCV200-6FG456C, so znani po njihovi sposobnosti za podporo hitremu prototipiranju.This device allows for quick design iterations and can be reconfigured in-field, which is an advantage for development cycles as it reduces time-to-market.It also adapts efficiently to changing requirements or updates in project specifications, ensuring that the final products are up-to-date with the latest technological standards.

Sposobnost integracije

Zmogljivosti integracije XCV200-6FG456C olajšajo konsolidacijo več diskretnih komponent v en sam čip.Ta integracija lahko privede do zmanjšane zapletenosti sistema, manjše porabe energije in prihrankov stroškov.By minimizing the number of separate components needed, this FPGA simplifies design processes and improves the reliability and compactness of the overall system.

XCV200-6FG456C dimenzije embalaže

The XCV200-6FG456C is a Field Programmable Gate Array (FPGA) from AMD's Virtex® series, housed in a 456-ball Fine-Pitch Ball Grid Array (FBGA) package.

• Vrsta paketa: 456-FBGA

• Velikost paketa: 23 mm x 23 mm

• Žoga: 1,0 mm

Proizvajalec XCV200-6FG456C

XCV200-6FG456C je terenski programirljivi vrat (FPGA), ki ga je prvotno razvil Xilinx, podjetje, znano po visokozmogljivih programirnih logičnih napravah.Po Xilinxovi pridobitvi Amd, XCV200-6FG456C je zdaj povezan z AMD kot njegovim sedanjim proizvajalcem.Vendar je ta model FPGA zastarel in ni več v proizvodnji.AMD še naprej podpira novejše arhitekture FPGA z izboljšano zmogljivostjo, učinkovitostjo moči in podaljšano dolgo življenjsko dobo, zaradi česar so sodobne alternative boljše za nove modele.

Zaključek

XCV200-6FG456C je vsestranska in hitra FPGA, ki je uporabna za številne tehnološke aplikacije.Čeprav se ne izdeluje več, je še vedno dobra izbira za starejše sisteme, ki potrebujejo zanesljive zmogljivosti.Ta vodnik je zajel svoj dizajn, korake programiranja in praktične uporabe, kar olajša razumevanje, kako deluje in kako se lahko uporablja.Ko bodo na voljo novejši FPGA, lahko to znanje izberete za pravo FPGA za vaše potrebe in izboljšate digitalne modele.

PDF podatkovnega lista

XCV200-6FG456C podatkovni listi:

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Pogosto zastavljena vprašanja [FAQ]

1. Kakšna je poraba energije XCV200-6FG456C?

XCV200-6FG456C deluje pri 2,5 V, z napetostnim območjem od 2.375V do 2,625V.Poraba energije je odvisna od logične uporabe in urna frekvence, vendar je kot starejša FPGA lahko manj učinkovita kot novejša naprava Xilinx.Upoštevati je treba pravilno upravljanje z močjo in odvajanje toplote.

2. Kako se XCV200-6FG456C primerja z XCV200-6FG256C?

XCV200-6FG456C ima večji paket (456-bal FBGA) v primerjavi z XCV200-6FG256C (FBGA s 256 kroglico), ki ponuja več V/I zatičev (284 proti 172) in potencialno boljše zmogljivosti za aplikacije, ki potrebujejo obsežno vmesnik.Če se vaš dizajn opira na več zmogljivosti V/I, je boljša izbira XCV200-6FG456C.

3. Ali lahko večkrat reprogramiram XCV200-6FG456C?

Da, XCV200-6FG456C je FPGA na osnovi SRAM, kar pomeni, da ga je mogoče reprogramirati neomejeno številokrat, kolikor je dobavljena moč.Vendar boste potrebovali zunanji nehlapni pomnilnik (EEPROM ali FLASH), da zadržite bitstream po napajalnem ciklu.

4. Ali XCV200-6FG456C podpira serijsko komunikacijo z visoko hitrostjo?

XCV200-6FG456C podpira več I/O standardov, kot so LVTTL, LVCMOS, PCI, GTL, HSTL in SSTL, vendar nima vgrajenih hitrih SERDE (serializer/deserializer) ali oddajniki, kot so sodobni FPGA.Za aplikacije, ki zahtevajo serijske povezave za visoke hitrosti (npr. PCIe, Gigabit Ethernet ali HDMI), upoštevajte novejše modele FPGA.

5. Kako se XCV200-6FG456C primerja z novejšimi modeli FPGA?

XCV200-6FG456C spada v starejšo generacijo FPGA.V primerjavi s sodobnim Virtex FPGA ima spodnje število vrat, počasnejše hitrosti ure in omejeno učinkovitost moči.Novejši modeli ponujajo večjo logično gostoto, bolj vgrajen pomnilnik, napredne bloke DSP in manjšo porabo energije, kar omogoča boljše za sodobne aplikacije.

AD73322AR pinout, funkcije in tehnične podrobnosti

na 2025/03/21

EP20K100EFC324-1X FPGA: Funkcije, specifikacije, aplikacije in vodnik za programiranje

na 2025/03/20

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/19 147783

-

USB-C pinout in funkcije

na 2000/04/19 112073

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/19 111352

-

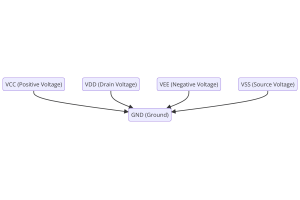

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/19 83833

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79646

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 67014

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63136

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63067

-

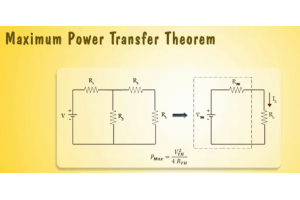

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54099

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52229