EP2S60F672C4 FPGA: Funkcije, aplikacije, programiranje in priročnik za podatkovni list

V tem priročniku boste dobili jasen pregled EP2S60F672C4, močnega FPGA iz Intelove družine Stratix II.Spoznali boste njegove glavne funkcije, arhitekturo, strukturo blokov in tehnične specifikacije, da boste razumeli, kako se prilega naprednim digitalnim dizajnom.Prav tako vas vodi skozi svoje programiranje, aplikacije, prednosti in slabosti, tako da lahko natančno vidite, kje in kako lahko to napravo uporabljate.Katalog

Kaj je EP2S60F672C4?

The EP2S60F672C4 je FPGA z visoko gostoto iz Intela (prej Altera), ki pripada družini Stratix II.Zgrajen na 90 nm, 1,2 V bakrenem SRAM procesu, prinaša veliko logično zmogljivost v paketu FBGA s 672 kroglici, zaradi česar je idealen za zapletene digitalne sisteme.V okviru serije EP2S naprava "60" sedi v območju med do zgornjim zgornjim delom linije Stratix II, ki ponuja močno ravnovesje logične gostote, vgrajenega pomnilnika in virov V/I.Ta FPGA, znana po svoji robustni arhitekturi in zanesljivosti, ostaja zaupanja vreden izbira v številnih naprednih modelih.

Iščete EP2S60F672C4?Pišite nam, da preverite trenutne zaloge, čas svinca in cene.

EP2S60F672C4 CAD modeli

EP2S60F672C4 simbol

Odtis EP2S60F672C4

EP2S60F672C4 3D model

Funkcije EP2S60F672C4

• Napredni postopek 90 nm, 1,2 V

EP2S60F672C4 je izdelan na 90 nm celotnem plastnem bakrenem procesu CMOS, ki deluje pri 1,2 V jedrne napetosti.Ta tehnologija omogoča veliko hitrost, zmanjšano porabo energije in večjo logično gostoto v primerjavi s starejšimi generacijami FPGA.

• Arhitektura prilagodljivega logičnega modula (alm)

Naprava uporablja milostinjo kot svoj logični gradnik namesto tradicionalnih logičnih elementov.Ta arhitektura izboljšuje porabo virov, kar omogoča učinkovito izvajanje bolj zapletenih logičnih funkcij v istem siliciju.

• Visoka logična gostota

FPGA s približno 60.440 logičnimi elementi (24.176 milostinja) podpira velike in prefinjene digitalne modele.Ta velika zmogljivost je primerna za aplikacije, kot so obdelava signalov, komunikacija in vgrajeni krmilni sistemi.

• Trimatrix ™ pomnilnik na čipu

EP2S60F672C4 združuje tri vrste blokov RAM-a (M512, M4K in M-RAM), da zagotovi skupno približno 2,4 mbit vgrajenega pomnilnika.Ta mešanica omogoča učinkovito izvajanje majhnih FIFO, srednjega medpomnilnika in velikih dvojnih spominov.

• Namenski DSP bloki

Naprava vključuje 36 namenskih blokov DSP, zasnovanih za aritmetične operacije, kot so množenje, akumulacije in filtriranje FIR.Ti bloki povečujejo zmogljivost pri računalniških intenzivnih nalogah, hkrati pa prihranijo splošne logične vire.

• Hitro V/I in celovitost signala

Podpira različne enomesečne in diferencialne V/I standarde, skupaj z dinamično fazno poravnavo (DPA).Te funkcije omogočajo stabilen prenos podatkov visoke hitrosti do 1 Gbps, kar zagotavlja zanesljivo komunikacijo z zunanjimi komponentami.

• Bogata podpora zunanjega pomnilniškega vmesnika

FPGA je združljiva z DDR, DDR2, QDR II, RLRAM II in drugimi pomnilniškimi standardi.Vgrajena podpora vmesnika poenostavlja oblikovanje plošče in dosega visoko pretok podatkov za intenzivne aplikacije.

• Prilagodljivo upravljanje ur

Do 12 PLL-jev na čipu omogočajo množenje ure, delitev, fazno prestavljanje in preklop brez napak.Domene ure lahko natančno prilagodite in zmanjšate tresenje, kar podpira notranje frekvence ure do 500–550 MHz.

• Šifriranje in rekonfiguracija bitstream

EP2S60F672C4 podpira bitstream šifriranje na osnovi AES za zagotovitev intelektualne lastnine.Ponuja tudi zmogljivost za oddaljeno konfiguracijo, ki omogoča posodobitve na terenu brez zamenjave naprave.

Blok diagram Stratix II

Blok diagram Stratix II, kot je prikazano za EP2S60F672C4, ponazarja notranjo razporeditev virov logike, pomnilnika in DSP, ki tvorijo jedro FPGA.Bloki logične matrike (laboratoriji) so razporejeni v običajni mreži, obdani z vgrajenimi stolpci RAM in DSP, ki zagotavljajo hitro aritmetiko in zmogljivosti za shranjevanje na čipu.Periferni V/I Elementi in urna omrežja uokvirjajo to strukturo, kar omogoča učinkovit prenos podatkov in časovni nadzor med FPGA in zunanjimi napravami.Ta diagram je pomemben, ker pomaga razumeti, kako so fizično organizirani različni funkcionalni bloki, kar jim omogoča optimizacijo namestitve, usmerjanja in splošne zmogljivosti sistema.

Diagram bank Stratix II I/O

Ta diagram bank Stratix II I/O prikazuje, kako so vhodni/izhodni zatiči EP2S60F672C4 razvrščeni in kakšni električni standardi podpirajo vsaka skupina.Vsaka V/I banka je zasnovana tako, da obravnava določene napetostne ravni, signalne vrste in funkcije, kot so LVTTL, SSTL, LVD -ji ali vhodni standardi ure.Postavitev prikazuje, kako so različne banke (npr. 1, 2, 5, 6 proti 3, 4, 7, 8 itd.) Optimizirane bodisi za diferencialno signalizacijo v Splošni v/I, bodisi s podporo za vhode LVDS/LVPECL na robovih.Razumevanje te strukture je pomembno pri dodeljevanju zatičev, saj pravilna izbira banke zagotavlja električno združljivost, poenostavi usmerjanje na plošči in poveča delovanje FPGA pri modelih visokih hitrosti.

Specifikacije EP2S60F672C4

|

Tip |

Parameter |

|

Proizvajalec |

Altera/Intel |

|

Serija |

STRATIX® II |

|

Embalaža |

Pladenj |

|

Status dela |

Zastarelo |

|

Število laboratorijev/CLB |

3022 |

|

Število logičnih elementov/celic |

60.440 |

|

Skupni ovnovski koščki |

2,544,192 |

|

Število V/I. |

492 |

|

Napetost - dovod |

1,15 V ~ 1,25 V |

|

Vrsta pritrditve |

Površinski nosilec |

|

Delovna temperatura |

0 ° C ~ 85 ° C (TJ) |

|

Paket / ohišje |

672-BBGA |

|

Paket dobaviteljskih naprav |

672-FBGA (27 × 27) |

|

Številka osnovnega izdelka |

EP2S60 |

Aplikacije EP2S60F672C4

1. digitalna obdelava signalov (DSP) in filtriranje

EP2S60F672C4 je zelo primeren za izvajanje visokozmogljivih funkcij DSP, kot so filtri FIR in IIR, obdelava FFT in zapletene aritmetične operacije.Njeni namenski bloki DSP učinkovito obravnavajo množenje in akumulacije, s čimer sproščajo splošne logične vire za druge naloge.Pomnilnik Trimatrix ™ na čipu omogoča gladko pufer in cevovod, kar je odlično za obdelavo v realnem času z visokimi hitrostmi vzorcev.Zaradi tega je naprava idealna za napredne aplikacije za zvočne, video in radarske signale.

2. Hitro komunikacija in mreženje

Vmesniki V/I in dinamične fazne poravnave (DPA) podpirajo vezje FPGA.Lahko implementira komunikacijske protokole in fizične plasti za sisteme, kot so usmerjevalniki, stikala in medsebojne povezave.S svojo veliko logično zmogljivostjo in prilagodljivimi PLL lahko upravlja s kompleksnimi pretvorbami časa in protokolov med več vmesniki za visoke hitrosti.Te zmogljivosti omogočajo, da se močno prilega telekomunikacijski infrastrukturi in omrežni opremi z visoko pasovno širino.

3. Krmilniki pomnilnika in sistemi za obdelavo podatkov

EP2S60F672C4 podpira različne zunanje pomnilniške vmesnike, vključno z DDR, DDR2, RLRAM II in QDR II, zaradi česar je idealen za oblikovanje krmilnikov pomnilnika z visoko pasovno širino.Z visokimi hitrostmi lahko z minimalnimi zamudami obvlada pufre podatkov, generacijo naslovov in arbitražo.Kombinacija omrežij hitre ure in vgrajenih blokov RAM -a omogoča učinkovito upravljanje velikih podatkovnih tokov.Zaradi tega je FPGA primerna za obdelavo slik, pretakanje videov in znanstvene računalniške platforme, ki se zanašajo na pretok močnih podatkov.

4. logika po meri in vgrajen pospešek

Z več kot 60.000 logičnimi elementi in bogatim upravljanjem ur lahko FPGA gosti prilagojene pospeševalnike strojne opreme za določene algoritme.Oblikovalci ga pogosto uporabljajo za nalaganje računalniško intenzivnih nalog iz procesorjev, kot so šifriranje, razčlenitev protokola ali kontrolne zanke v realnem času.Prav tako lahko integrira več funkcionalnih blokov, zaradi česar je primeren za zapletene soc-podobne modele.Ta prilagodljivost je dragocena v aplikacijah, kot so industrijska avtomatizacija, varnostni sistemi in enote za nadzor vesoljskega vesolja.

5. Platforme za prototipiranje in izobraževalne razvojne platforme

Naprava EP2S60 se običajno najde v razvojnih kompletih FPGA, ki se uporabljajo za prototipiranje, testiranje in akademske raziskave.Njegovo ravnotežje logične zmogljivosti, število V/I in DSP zmogljivosti omogočajo inženirjem in študentom, da izvajajo in preverjajo polne sisteme na enem samem čipu.Podpira hitro ponovitev digitalnih modelov, ki omogoča preverjanje strojne opreme, preden se zaveže k razvoju ASIC.Številne univerze in laboratoriji za raziskave in razvoj ga uporabljajo za poučevanje naprednih konceptov digitalnega oblikovanja in obdelave signalov.

EP2S60F672C4 Podobni deli

|

Specifikacija |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Družina / serija |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Logični elementi (LE) |

60.440 |

60.440 |

60.440 |

60.440 |

60.440 |

60.440 |

|

Milostinjo |

24.176 |

24.176 |

24.176 |

24.176 |

24.176 |

24.176 |

|

Paket |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Hitrost |

C4 (std) |

C3 (hitreje) |

C5 (hitreje) |

C5 (hitreje) |

I4 (std) |

I3 (hitreje) |

|

Temperaturna ocena |

Komercialna (0 ~ 70 ° C) |

Komercialna |

Komercialna |

Komercialna |

Industrijsko (−40 ~ 100 ° C) |

Industrijsko (−40 ~ 100 ° C) |

|

I/o zatiči |

492 |

492 |

492 |

492 |

492 |

492 |

|

Pomnilnik na čipu |

2,4 MBIT |

2,4 MBIT |

2,4 MBIT |

2,4 MBIT |

2,4 MBIT |

2,4 MBIT |

|

Jedrna napetost |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

|

Ključna razlika |

Osnovna komercialna hitrost |

C3 Speed Ben, brez svinca "N" |

Koš za večjo hitrost |

Korianta z višjo hitrostjo, "N" |

Industrijska temperatura, enaka gostota |

Industrijska, hitrejša hitrost, brez svinca |

Koraki programiranja EP2S60F672C4

Preden lahko v svoji zasnovi uporabite EP2S60F672C4 FPGA, ga morate pravilno konfigurirati s sestavljenim bitstream.Ta postopek vključuje pripravo programske datoteke, nastavitev vmesnika strojne opreme in zagotavljanje, da se konfiguracija pravilno naloži pri vklopu.

1. korak: Ustvarite in sestavite svoj dizajn

Začnete z razvojem logične zasnove s programsko opremo Intel Quartus II.Po dokončanju zasnove ga sestavite tako, da ustvarite programsko datoteko (.SOF ali .POF) posebej za napravo EP2S60F672C4.Postopek kompilacije preverja čas za časovno razporeditev, naloge PIN in porabo virov, da se zagotovi, da se vaš dizajn ustreza v arhitekturi FPGA.Ko je sestavljen, je vaš bitstream pripravljen za konfiguracijo naprave.

2. korak: Nastavite programsko opremo

Nato pripravite vmesnik za fizično programiranje med računalnikom in ploščo FPGA.Običajno to vključuje povezovanje USB-Blasterja ali združljivega kabla JTAG na vrata JTAG naprave.Preverite, ali Quartus II prepozna programerja in da je ciljna naprava pravilno zaznana.Ta korak zagotavlja stabilno komunikacijo pred začetkom konfiguracijskega postopka.

3. korak: Naložite programsko datoteko v napravo

Z orodjem programerja Quartus II dodate zbrano datoteko .SOF ali .POF in na seznamu zaznanih naprav izberete EP2S60F672C4.Nato sprožite programsko zaporedje, med katerim se bitstream prenese in naloži v konfiguracijske celice SRAM FPGA.Če želite potrditi uspešno konfiguracijo, morate spremljati vrstico za napredek in status.Ko je končana, FPGA začne takoj izvajati programirano logiko.

4. korak: Preverite konfiguracijo in delovanje

Po programiranju preverite, ali naprava deluje po načrtih.Quartus II ponuja možnost preverjanja za preverjanje konfiguracijskih CRC in statusnih signalov, s čimer zagotavlja, da se zasnova pravilno naloži.Prav tako lahko preizkusite funkcije V/I ali zaženete funkcionalno simulacijo za potrditev vedenja sistema.Ta zadnji korak zagotavlja, da je vaš dizajn v celoti operativen in stabilen na strojni opremi.

EP2S60F672C4 Prednosti in slabosti

Prednosti

• Visoka logična gostota za zapletene zasnove

• Dobro razmerje med uspešnostjo in stroški

• Enostavna migracija znotraj iste družine

• Stabilna in zrela razvojna orodja

• Dokazana zanesljivost pri industrijski uporabi

Slabosti

• zastarel in težje

• Večja poraba energije kot novejši FPGA

• Brez sodobnih hitrih oddajnikov

• Težje zapiranje časa pri visoki uporabi

• Omejena razširljivost za prihodnje protokole

EP2S60F672C4 Dimenzije embalaže

|

Tip |

Parameter |

|

Vrsta paketa |

672-FBGA (Fineline BGA) |

|

Velikost telesa (L × W) |

27,00 mm × 27,00 mm |

|

Skupna višina paketa (a) |

Max 3,50 mm |

|

Višina (A1) |

Min 0,30 mm |

|

Debelina substrata (A2) |

Največ 3,00 mm |

|

Premer kroglice (b) |

0,50 mm - 0,70 mm |

|

Žoga (e) |

1,00 mm |

|

Število kroglic |

672 |

|

Slog pritrditve |

Površinski nosilec |

|

Opis paketa |

FBGA, 27 × 27 mm mreža |

EP2S60F672C4 Proizvajalec

EP2S60F672C4 FPGA izdeluje Altera Corporation, vodilni pionir v programirljivih logičnih napravah.Leta 2015 je Altera pridobila Intel, in izdelek zdaj spada v Intelovo programirljivo skupino rešitev (PSG), ki še naprej podpira in oskrbuje ustaljene družine FPGA.Intel vzdržuje linijo Stratix II kot del svojega zapuščenega portfelja izdelkov, s čimer zagotavlja dokumentacijo, podporo orodij in dolgoročno razpoložljivost za industrijske in komunikacijske aplikacije.

Zaključek

EP2S60F672C4 združuje visoko logično gostoto, fleksibilno pomnilniško arhitekturo in robustne funkcije V/I za podporo zapletenim digitalnim sistemom.Njegova zasnova, ki temelji na ALM, Trimatrix ™ pomnilnik, bloki DSP in funkcije upravljanja ur omogočajo učinkovito izvajanje zahtevnih aplikacij.Medtem ko ponuja dokazano zanesljivost in zrelo razvojno podporo, se sooča z omejitvami, kot sta zastarelost in pomanjkanje sodobnih oddajnikov v primerjavi z novejšimi generacijami FPGA.Na splošno zaradi uravnotežene zmogljivosti in vsestranskosti omogočajo trdno izbiro za obdelavo signalov, komunikacijo, ravnanje s podatki in prototipiranje aplikacij.

PDF podatkovnega lista

EP2S60F672C4 podatkovni listi:

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Pogosto zastavljena vprašanja [FAQ]

1. Ali lahko EP2S60F672C4 deluje s sodobnimi pomnilniškimi vmesniki DDR?

Da, podpira vmesnike DDR, DDR2, QDR II in RLRAM II, ki pokrivajo številne skupne standarde zunanjega pomnilnika.Zaradi tega je primeren za aplikacije za obdelavo podatkov z visoko pasovno širino.

2. Ali EP2S60F672C4 zahteva posebno ravnanje ali shranjevanje?

Da, tako kot druge komponente, ki jih pakirajo BGA, jih je treba shraniti v embalažo, ki jo nadzoruje vlaga, in ravnati z zaščito ESD.Upoštevanje ustreznih praks shranjevanja pomaga ohranjati spajkalnost in zanesljivost naprav med montažo.

3. Kako lahko zmanjšate porabo energije v modelih EP2S60F672C4?

Lahko optimizirate logično uporabo, neuporabljene ure vrat, nižje V/I napetosti, kjer je to mogoče, in izkoristite možnosti sinteze, ki se zaveda moči v Quartusu II, da zmanjšate skupno vleko moči.

4. Katera programska orodja so potrebna za EP2S60F672C4?

Za konfiguracijo naprave boste potrebovali programsko opremo Intel Quartus II za oblikovanje, kompilacijo in programiranje, skupaj z USB-Blasterjem ali združljivim kablom JTAG.

5. Ali EP2S60F672C4 podpira posodobitve na terenu ali na daljavo?

Da, podpira bitstream šifriranje in daljinsko rekonfiguracijo, ki temelji na AES, kar omogoča varno posodobitev sistema, ne da bi fizično zamenjali FPGA.

Vse o LFXP6C-3FN256C rešetka

na 2025/10/6

XC2C256-7TQ144C CPLD: pinout, funkcije, programiranje in vodnik za podatkovni list

na 2025/10/3

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/19 147782

-

USB-C pinout in funkcije

na 2000/04/19 112062

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/19 111352

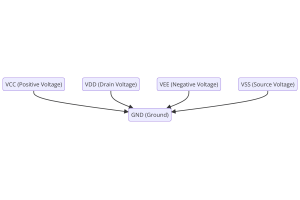

-

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/19 83819

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79639

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66999

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63124

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63062

-

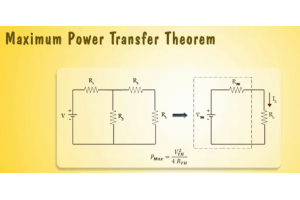

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54097

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52215