XC2C256-7TQ144C CPLD: pinout, funkcije, programiranje in vodnik za podatkovni list

V tem priročniku boste jasno pogledali XC2C256-7TQ144C, CPLD z nizko močjo iz družine CoolRunner-II Xilinx (zdaj AMD).Spoznali boste njegovo konfiguracijo PIN, CAD modele in glavne funkcije, kot so logična zmogljivost, možnosti V/I, napetostne podpore in funkcije varčevanja z močjo.Sprehodili se bomo tudi po njegovi arhitekturi, I/V krivulji in specifikacijah, ki jim sledijo aplikacije, podobni deli, koraki programiranja, prednosti in slabosti, podrobnosti embalaže in informacije o proizvajalcu, tako da lahko natančno razumete, kako se ta naprava prilega vašim projektom.Katalog

Kaj je XC2C256-7TQ144C?

The XC2C256-7TQ144C je CPLD z nizko močjo (zapletena programirljiva logična naprava) iz Xilinxove družine CoolRunner-II, ki je zdaj del AMD.Odlikuje ga 256 makrocelic in je na voljo v 144-polnem paketu TQFP, zasnovan za hitro, determinirano delovanje z minimalno porabo energije.Deluje na 1,8 V jedru, ponuja zanesljive zmogljivosti v kompaktnem faktorju oblike in je dobro primeren za modele, ki zahtevajo takojšnjo zmogljivost in učinkovito izvajanje logike.V okviru vsestranske serije Colrunner-II ima koristi od preizkušene arhitekture in široke združljivosti dizajna.

Iščete XC2C256-7TQ144C?Pišite nam, da preverite trenutne zaloge, čas svinca in cene.

XC2C256-7TQ144C Diagram

Diagram PIN-Out-Out-Out-Out Diagram XC2C256-7TQ144C prikazuje, kako so razporejeni 144 zatičev za napajanje, ozemljitev, JTAG in uporabniško v/I funkcije.Večina zatičev je V/I, ki jih je mogoče konfigurirati kot vhodi ali izhode in jih enakomerno porazdelijo, da podpirajo prilagodljivo usmerjanje.VCC, VCCIO1, VCCIO2, Vaux in GND zatiči so nameščeni okoli paketa, da se zagotovi stabilna porazdelitev moči in več možnosti V/I napetosti.Zatiči JTAG (TDI, TDO, TMS, TCK) so združeni za enostavno programiranje in testiranje v sistemu.

XC2C256-7TQ144C CAD modeli

Simbol XC2C256-7TQ144C

XC2C256-7TQ144C FISPInt

XC2C256-7TQ144C 3D model

Funkcije XC2C256-7TQ144C

• Vrsta naprave in družina

XC2C256-7TQ144C je zapletena programabilna logična naprava (CPLD), ki spada v družino CoolRunner-II, ki jo je razvil Xilinx (zdaj AMD).Zasnovan je za nizko porabo energije, hkrati pa ohranja hitro, deterministično logično delovanje, zaradi česar je idealen za kontrolno logiko in povezavo.

• Logična zmogljivost

Ta naprava vsebuje 256 makrocelic, ki so programirljivi logični viri v CPLD.Te makrocelice je mogoče konfigurirati za izvajanje različnih kombiniranih in zaporednih logičnih funkcij, kar daje zmerno zmogljivost za nadzor, logiko lepila in vmesnike vodila.

• Logični bloki (funkcijski bloki)

Vključuje 16 funkcijskih blokov, ki organizirajo in upravljajo skupine makrocelic.Vsak blok ponuja lokalne vire medsebojne povezave in izdelkov, kar omogoča prilagodljivo logično izvajanje in učinkovito usmerjanje znotraj naprave.

• Uporabniški V/I zatiči

XC2C256-7TQ144C ponuja do 118 uporabniških zatičev, ki jih je mogoče konfigurirati v svojem paketu TQFP-144.To visoko število PIN omogoča, da se naprava hkrati poveže z več podsistemi, zaradi česar je primerna za zapletene modele na ravni plošče.

• Jedrna napetost (VCC)

Jedro deluje na nominalnem 1,8 V (1,7 V do 1,9 V območja), kar pomaga zmanjšati porabo energije v primerjavi s starejšimi 5 V CPLD.Ta nižja napetost je uporabna v sodobnih digitalnih sistemih z mešano napetostjo.

• Več-napetost V/I podpora

Banke V/I podpirajo več napetostnih standardov, vključno z 1,5 V, 1,8 V, 2,5 V in 3,3 V. Ta prilagodljivost omogoča CPLD, da neposredno povezuje komponente, ki delujejo na različnih stopnjah napetosti brez zunanjih prestavkov.

• Delovanje visoke hitrosti

Naprava z značilno zamudo širjenja od pin-pin približno 5,7 ns (hitrost "-7") naprava zagotavlja hitro, determinirano delovanje.Zaradi tega je primerna za časovne kritične aplikacije, kot so dekodiranje naslovov, arbitraža avtobusa in nadzor.

• Nizka poraba energije

Serija Coodrunner-II je znana po izjemno nizkih tokovih v pripravljenosti, pogosto v mikroamp območju.Ta nizka statična moč v kombinaciji z dinamičnimi funkcijami varčevanja z močjo omogoča učinkovito uporabo XC2C256-7TQ144C v sistemih z baterijo ali vedno v sistemih.

• Tehnologija podatkovnega podatkov

Ta funkcija omogoča odmik neuporabljenih vhodov, preprečuje nepotrebno preklop in zmanjšanje dinamične porabe energije.V aplikacijah je dragoceno, kjer so določeni signali dolgo neaktivni.

• Programiranje JTAG v sistemu

Naprava podpira IEEE 1149.1 (JTAG) in IEEE 1532 za programiranje v sistemu.To pomeni, da je CPLD mogoče konfigurirati, preizkusiti in reprogramirati, ne da bi ga odstranili s plošče, kar poenostavi razvoj in posodobitve.

• Napredna konstrukcija ure

XC2C256-7TQ144C vključuje več globalnih ur, delilnikov ur in dvojnih sproženih registrov.Omogoča tudi globalni nabor/ponastavitev in lokalno ure na makrocelino, kar omogoča prožen nadzor nad časovnim razporedom in sinhronizacijo.

• Vhodi Schmitt-Trigger

Izbrane vhodne zatiče je mogoče konfigurirati, ko Schmitt sproži za izboljšanje imunosti hrupa.To je koristno za ravnanje s počasnimi ali hrupnimi vhodnimi signali, ne da bi dodali zunanje kondicioniranje.

• Prilagodljive izhodne funkcije

Izhodi podpirajo delovanje v treh državah, krmiljenje hitrosti, zadrževanje vodila, konfiguracije z odprtim odtokom in neobvezne vleke.Te možnosti olajšajo prilagajanje CPLD različnim standardom vodila in zunanje obremenitve.

• Napredna matrica medsebojne povezave (AIM)

Napredna matrica medsebojne povezave učinkovito povezuje funkcijske bloke, ki zagotavljajo popolno usmerjanje izdelkov po napravi.To izboljša prilagodljivost logike in pomaga ohranjati predvidljivo učinkovitost časa.

CoolRunner-II CPLD arhitektura

Arhitektura CoolRunner-II CPLD arhitekture XC2C256-7TQ144C je zgrajena okoli funkcijskih blokov, V/I blokov in napredne matrike medsebojne povezave (AIM).Vsak funkcijski blok vsebuje makrocelice in programirljivo logično matriko (PLA), ki izvajajo uporabniško definirano logiko, medtem ko AIM učinkovito usmerja signale med bloke.V/I bloki povezujejo notranjo logiko z zunanjimi zatiči ter namensko programiranje in testiranje v sistemu JTAG in BSC/ISP vezja.Ta strukturirana in medsebojno povezana arhitektura omogoča hitre, deterministične zmogljivosti z nizko porabo energije, zaradi česar je idealen za nadzor, povezovanje in logiko lepila v digitalnih sistemih.

Tipična I/V krivulja za XC2C256

Tipična I/V krivulja za XC2C256-7TQ144C prikazuje razmerje med izhodno napetostjo (VO) in izhodnim tokom (IO) za različne napajalne napetosti v/I (1,5 V, 1,8 V, 2,5 V in 3,3 V).Ko se napajalna napetost povečuje, lahko naprava navaja ali potopi višje tokove, preden izhodna napetost začne znatno padati.To vedenje je pomembno za razumevanje sposobnosti pogona CPLD pri povezovanju z zunanjimi komponentami, pri čemer zagotavlja, da ravni signala ostanejo veljavne pod obremenitvijo.Mnogi uporabljajo to krivuljo, da izberejo ustrezne napetosti v/I in zagotavljajo zanesljivo delovanje v aplikacijah, ki zahtevajo posebne trdnosti, ki vozijo tok.

Specifikacije XC2C256-7TQ144C

|

Tip |

Parameter |

|

Proizvajalec |

AMD/XILINX |

|

Serija |

Colrunner II |

|

Embalaža |

Pladenj |

|

Status dela |

Zastarelo |

|

Programirani tip |

V sistemskem programiranju |

|

Čas zamude TPD (1) Max |

6.7 ns |

|

Napajanje napetosti - notranja |

1,7 V ~ 1,9 V |

|

Število logičnih elementov/blokov |

16 |

|

Število makrocelic |

256 |

|

Število vrat |

6000 |

|

Število V/I. |

118 |

|

Delovna temperatura |

0 ° C ~ 70 ° C (TA) |

|

Vrsta pritrditve |

Površinski nosilec |

|

Paket / ohišje |

144-LQFP

|

|

Paket dobaviteljskih naprav |

144-TQFP (20 × 20) |

|

Številka osnovnega izdelka |

XC2C256 |

Aplikacije XC2C256-7TQ144C

1. Logika lepila in premostitev vmesnika

XC2C256-7TQ144C je idealen za izvajanje logike lepila, ki povezuje in koordinira signale med različnimi digitalnimi komponentami.Lahko se ukvarja s funkcijami, kot so dekodiranje naslovov, arbitraža avtobusa in prevajanje protokolov, kar omogoča gladko komunikacijo med mikrokontrolerji, pomnilnikom, senzorji in drugimi perifernimi napravami.Njegova predvidljiva časovna razporeditev in hitre zamude pri pin-pin zagotavljajo zanesljivo povezovanje tudi v zapletenih modelih plošč.

2. naprave z nizko močjo in baterijo

Zahvaljujoč tehnologiji Fast Zero Power (FZP) in zelo nizkemu pripravljenosti, je ta CPLD zelo primeren za prenosno in baterijsko elektroniko.Lahko ostane neprekinjeno, medtem ko porabi minimalno energijo, zaradi česar je popolna za vedno nadzorovalno ali nadzorovalno vezje.Nadalje zmanjšate porabo električne energije s funkcijami, kot je DataGate, kar minimizira dinamično preklop, ko so vhodi neaktivni.

3. Nadzorna logika in zaporedje

Naprava se odlično odreže pri izvajanju strojev s končnim stanjem, nadzoru časa in sekvenciranju signala, potrebnih v številnih vgrajenih sistemih.Njegova determinirana, nehlapna arhitektura omogoča, da se krmilna logika aktivna takoj po vklopu brez zamud konfiguracije.Zaradi tega je močna izbira za ponastavitev logike, vezja za stiskanje rok in drugih časovno kritičnih nalog.

4. Vgrajena sistemska podpora in periferna logika

V vgrajenih modelih lahko XC2C256-7TQ144C deluje kot prilagodljiv podporni čip, izvaja specializirane vmesnike ali razširi zmogljivosti mikrokontrolerja.Lahko obravnava komunikacijske protokole, kot so SPI, I²C ali UART, ustvarijo izbire čipov ali upravljajo z prekinitvijo.Z izklopom teh funkcij iz CPU -ja poenostavi razvoj vdelane programske opreme in izboljša splošno delovanje sistema.

XC2C256-7TQ144C Podobni deli

|

Specifikacija |

XC2C256-7TQ144C |

XC2C256-7TQ144I |

XC2C256-7TQG144I |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

Družina naprav |

CoolRunner-II CPLD |

CoolRunner-II CPLD |

CoolRunner-II CPLD |

CoolRunner-II CPLD |

CoolRunner-II CPLD |

CoolRunner-II CPLD |

|

Logična gostota (makrocelice) |

256 |

256 |

256 |

256 |

256 |

256 |

|

Vrsta paketa |

TQFP-144 |

TQFP-144 |

TQFP-144 (brez PB) |

VQFP-100 |

VQFP-100 (brez PB) |

TQFP-144 |

|

Hitrost |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (hitreje) |

|

Temperaturno območje |

Komercialna (0 - 70 ° C) |

Industrijsko (-40-85 ° C) |

Industrijsko (-40-85 ° C) |

Komercialna (0 - 70 ° C) |

Komercialna (0 - 70 ° C) |

Komercialna (0 - 70 ° C) |

|

Število PIN -a I/O. |

118 |

118 |

118 |

80 |

80 |

118 |

|

Jedrna napetost (VCC) |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

|

V/I napetostna podpora |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

|

Skladnost / brez PB |

Standardno |

Standardno |

Brez PB / ROHS |

Standardno |

Brez PB / ROHS |

Standardno |

|

Razlike |

Osnovna komercialna različica |

Različica industrijske temp |

Industrijska + različica brez PB |

Manjši paket, manj V/I |

Manjša različica brez PB |

Hitrejša časovna različica |

Koraki programiranja XC2C256-7TQ144C

Programiranje XC2C256-7TQ144C je preprost postopek, ki vključuje pripravo vašega dizajna, ustvarjanje programske datoteke in nalaganje v CPLD prek JTAG.Če natančno sledite vsakemu koraku, lahko na plošči zagotovite uspešno konfiguracijo in pravilno delovanje naprave.

1. zasnovo in sintetiziranje

Začnete s pisanjem logične zasnove z uporabo HDL (VHDL ali Verilog) ali shematičnega vnosa.Po zaključku zasnove zaženete postopek sinteze, ki pretvori vašo logiko v notranjo strukturo makrocelic in medsebojnih povezav naprave.Ta korak zagotavlja, da je vaš dizajn združljiv z arhitekturo XC2C256 in pripravljen za izvajanje.

2. Kraj in pot / izvajanje (prileganje)

Nato izvajate kraj in pot, znano tudi kot prileganje, ki dodeli vašo sintetizirano logiko dejanskim fizičnim makrocelikom in usmerjanjem virov znotraj CPLD.Orodje preverja omejitve časovne omejitve, rešuje porabo virov in optimizira poti, da doseže delovanje vašega dizajna.To zagotavlja, da se bo vezje zanesljivo potekalo, ko bo programirano v napravo.

3. Ustvari programsko datoteko

Ko je implementacija končana, ustvarite programsko datoteko (bit, Jam ali SVF format), ki vsebuje natančne konfiguracijske podatke za napravo.Ta datoteka predstavlja, kako je vsaka makrocelica, Interconnect in V/I nastavljena za izvajanje vaše logike.Pripravite se ta datoteka, preden nadaljujete na dejansko programiranje naprave.

4. JTAG / VSSISTEM programira

Končno napravo povežete s računalnikom s kablom JTAG programiranja in odprete orodje Xilinx Impact (ali enakovredno).Nato naložite ustvarjeno programsko datoteko in jo prenesete na XC2C256-7TQ144C prek zatičev JTAG (TDI, TDO, TCK, TMS).Ko je postopek končan, CPLD takoj začne delovati s programirano logiko, ne da bi potreboval napajalni cikel ali zunanji konfiguracijski pomnilnik.

Prednosti in slabosti XC2C256-7TQ144C

Prednosti

• Zelo nizka moč pripravljenosti, idealna za modele, ki jih poganja baterijo.

• Takojšnja operacija brez konfiguracijske zamude.

• Predvidljiv čas za lažje zapiranje oblikovanja.

• Nadomešča več diskretnih logičnih čipov, shranjevanje prostora in stroškov.

• Podpira več V/I napetosti brez zunanjih prestavkov.

Slabosti

• Omejena logična zmogljivost v primerjavi z večjimi CPLD ali FPGA.

• Brez vgrajenih oddajnikov DSP, RAM-a ali hitrih hitrosti.

• Zastarela, oteževanje prihodnjega pridobivanja.

• Nižja zgornja meja zmogljivosti za hitre aplikacije.

• manj prilagodljivosti usmerjanja za zapletene ali nepravilne modele.

XC2C256-7TQ144C Dimenzije embalaže

|

Tip |

Parameter |

|

Vrsta paketa |

TQFP-144 |

|

Velikost telesa paketa |

20 mm × 20 mm |

|

Svinčeno igrišče |

0,5 mm |

|

Število zatičev |

144 |

|

Višina paketa (max) |

1,4 mm |

|

Debelina paketa (nominalna) |

1,0 mm |

|

Dolžina svinca |

0,45 mm ~ 0,75 mm |

|

Širina svinca |

0,17 mm ~ 0,27 mm |

|

Vrsta pritrditve |

Površinski nosilec |

|

Paket dobaviteljskih naprav |

144-TQFP (20 × 20) |

Proizvajalec XC2C256-7TQ144C

XC2C256-7TQ144C izdeluje Xilinx, vodilno podjetje v programirljivih logičnih rešitvah.Xilinx je splošno priznan za pionirske tehnologije FPGA in CPLD, ki zagotavlja zanesljive in visokozmogljive naprave za industrijske, komercialne in potrošniške aplikacije.Danes Xilinx deluje kot del Amd, še naprej zagotavljajo napredne programirljive logične izdelke z močno dolgoročno podporo in inovacijami.

Zaključek

XC2C256-7TQ144C izstopa za svojo nizko porabo energije, hitro determinirano zmogljivost in večkratno prilagodljivost V/I, zaradi česar je zanesljiva izbira za sodobne digitalne modele.Njegova uravnotežena kombinacija 256 makrocelic, 118 V/I zatičev in napredne arhitekture Interconnect podpira široko paleto nadzora, povezovanja in logičnih funkcij.S podporo za programiranje v sistemu, funkcijami za varčevanje z močjo in robustne konfiguracije V/I se gladko integrira v vgrajene sisteme in mešano napetostno okolje.

PDF podatkovnega lista

XC2C256-7TQ144C podatkovni listi:

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Pogosto zastavljena vprašanja [FAQ]

1. Ali XC2C256-7TQ144C zahteva zunanji konfiguracijski pomnilnik?

Ne. Ena od njegovih prednosti je takojšnje delovanje.Konfiguracija je shranjena notranje, zato je pripravljena za zagon brez zunanjega maturantskega maturantskega plesa ali bliskovnega pomnilnika.

2. Katera programska orodja so združljiva z XC2C256-7TQ144C?

Napravo lahko programirate s programsko opremo XIlinx Impact s kablom JTAG Programming.Mnogi uporabljajo tudi združljive programerje JTAG tretjih oseb, vendar se prepričajte, da podpirajo standarde IEEE 1149.1/1532.

3. Ali lahko XC2C256-7TQ144C v vašem dizajnu nadomesti več diskretnih logičnih ICS?

DA.Ta CPLD lahko s svojimi 256 makroceli in prilagodljivimi V/I vključi več logike lepila in krmiljenja lepila v eno napravo, kar vam pomaga zmanjšati prostor plošče in število komponent.

4. Ali je XC2C256-7TQ144C primeren za aplikacije z nizko močjo baterije?

DA.Zahvaljujoč svoji tehnologiji Fast Zero Power (FZP) in zelo nizkemu pripravljenosti, je idealen za vedno vklopljena vezja, prenosne naprave in vgrajene sisteme, ki so občutljivi na moč.

5. Ali lahko uporabite XC2C256-7TQ144C za obdelavo signalov za visoko hitrost?

Ni zasnovan za naloge DSP za visoke hitrosti ali oddajnike.Medtem ko prinaša hitre zamude pri pin-pin, je najbolj primerna za nadzor, povezovanje in časovno logiko, ne za zapleteno obdelavo podatkov.

EP2S60F672C4 FPGA: Funkcije, aplikacije, programiranje in priročnik za podatkovni list

na 2025/10/4

Pregled EPM3256AFC256-7 CPLD: Funkcije, pinout, programiranje in aplikacije

na 2025/10/3

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/18 147770

-

USB-C pinout in funkcije

na 2000/04/18 112006

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/18 111351

-

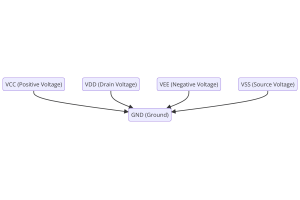

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/18 83768

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79564

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66959

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 63098

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63040

-

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54096

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52184