LFEC3E-3Q208C FPGA Pregled: Funkcije, aplikacije, programiranje in specifikacije

V tem članku boste izvedeli o LFEC3E-3Q208C, FPGA iz Lattice Semiconductor.Videli boste, kaj je, glavne funkcije, ki jih ponuja, in zakaj je uporabna za številne modele srednjega razreda.Vsebina vas vodi tudi skozi njene specifikacije, aplikacije in korak za korakom po postopku programiranja, skupaj s svojimi prednosti, slabostmi in podrobnostmi proizvajalca.Katalog

Kaj je LFEC3E-3Q208C?

The LFEC3E-3Q208C je stroškovno učinkovit poljski programiran matrični niz (FPGA) iz Lattice Semiconductor, zasnovan kot del družine Latticeec (Economy).Ta družina je bila razvita za zagotavljanje programirljivih logičnih rešitev, ki uravnotežijo cenovno dostopnost z zanesljivimi zmogljivostmi za glavne modele.Znotraj hierarhije Latticeec sedi v srednjem razredu in ponuja približno 3000 logičnih elementov in učinkovito porabo energije, ki premosti vrzel med manjšimi vhodnimi napravami in večjimi, bolj intenzivnimi viri.Širša serija LatticeECP/EC poudarja nizkocenovno programirljivost, razširljivost in prilagodljivost v več velikostih naprav, pri čemer se varianta EC osredotoča na učinkovitost, ki temelji na ekonomiji.

Iščete LFEC3E-3Q208C?Pišite nam, da preverite trenutne zaloge, čas svinca in cene.

LFEC3E-3Q208C LASTNOSTI

• Logični viri

Naprava integrira približno 3100 logičnih elementov, organiziranih v 384 blokov, kar ji daje dovolj zmogljivosti za modele srednjega dosega.To ravnovesje virov je primerno za kontrolno logiko, obdelavo signalov in vgrajene aplikacije brez prekomernih stroškov.

• Programirani I/O.

Z do 145 programirljivimi vhodnimi/izhodnimi zatiči podpira najrazličnejše možnosti povezljivosti.Ti I/OS so združljivi z več standardi, kot so LVCMOS, LVTTL, LVDS, PCI in SSTL, kar omogoča fleksibilno sistemsko integracijo.

• Vgrajen pomnilnik

FPGA vključuje namenski blok RAM (EBR) in porazdeljene RAM-ove vire, ki zagotavljajo učinkovito shranjevanje na čipu.To omogoča implementacijo medpomnilnika podatkov, iskalnih tabel ali majhnih vgrajenih spominov neposredno znotraj naprave.

• Upravljanje ur

Odlikuje ga do štiri integrirane PLL, ki ponujajo frekvenčno množenje, delitev in fazno premikanje.To omogoča natančen nadzor in sinhronizacijo za modele za visoke hitrosti.

• Podpora za pomnilnik DDR

Naprava vključuje podporo strojne opreme za vmesnike DDR, ki lahko zažene DDR400 (200 MHz).Zaradi tega je praktično za modele, ki zahtevajo zunanji dostop do hitrega pomnilnika.

• Učinkovitost moči

FPGA, ki deluje z 1,2 V jedrni, zmanjšuje skupno porabo energije sistema.Njegova zasnova z nizko močjo je idealna za prenosne ali energijsko občutljive aplikacije.

• Funkcije na ravni sistema

Vgrajene funkcije, kot so IEEE 1149.1 mejne skeniranje, analiza logike na čipu (isptracy) in vmesnik SPI Boot Flash, poenostavijo testiranje in odpravljanje napak.Te lastnosti zmanjšujejo čas razvoja in izboljšajo zanesljivost oblikovanja.

• Razvojna podpora

Naprava, ki jo podpira ISPlever Design Suite, koristi od avtomatiziranih sintez, orodij za preverjanje in route in preverjanja.Za pospešitev skupnih funkcij in skrajšanje časa na trg lahko uporabite tudi IP bloke ISpleverCore.

Diagram družinskega bloka LatticeECP/ES

Blok diagram družine LatticeECP/EC (vključno z LFEC3E-3Q208C) prikazuje, kako je zgrajena FPGA in kako delujejo njeni deli.Programibilne V/I celice (PICS) so nameščene po robovih, da se čip poveže z zunanjimi napravami, kar podpira številne signalne standarde.V notranjosti programirljive funkcionalne enote (PFU) obravnavajo logične operacije, pri čemer so nekatere seznanjene z vgrajenim blokom RAM (EBR) za shranjevanje podatkov, druge pa so osredotočene le na logiko.Sysclock PLLS upravlja s signali ure, tako da lahko zasnova deluje s pravo hitrostjo in časovnim razporedom.Port Sysconfig in pristanišče JTAG vam omogočata, da programirate, preizkusite in odpravljate odpravljanje napak FPGA.Ta postavitev daje prilagodljivost LFEC3E-3Q208C, zanesljive zmogljivosti in preprosto integracijo v stroškovno občutljive modele.

Diagram rezine LatticeECP/EC

Rezina v družini LatticeECP/EC, kot v LFEC3E-3Q208C, je temeljna logična enota, ki združuje bloke LUT4 in nosil za izvajanje logike in aritmetičnih operacij.Vsaka rezina vključuje tudi flip-flops/zaklepe za shranjevanje podatkov in omogočanje zaporedne logike, pri čemer multipleksarji lahko signale prilagodite bodisi prek registrov bodisi neposredno.Ta struktura je pomembna, ker daje hitrost, prilagodljivost in učinkovitost FPGA za obvladovanje preprostih in zapletenih digitalnih modelov.Naslednja tabela povzema opise signala rezine, vključno z njihovimi funkcijami, vrstami, imeni signalov in namene.

|

Delovanje |

Tip |

Imena signalov |

Opis |

|

Vnos |

Podatkovni signal |

A0, b0, c0, d0 |

Vhodi v LUT4 |

|

Vnos |

Podatkovni signal |

A1, b1, c1, d1 |

Vhodi v LUT4 |

|

Vnos |

Večnamensko |

M0 |

Večnamenski vhod |

|

Vnos |

Večnamensko |

M1 |

Večnamenski vhod |

|

Vnos |

Kontrolni signal |

Ce |

Ura omogoči |

|

Vnos |

Kontrolni signal |

LSR |

Lokalni komplet/ponastavitev |

|

Vnos |

Kontrolni signal |

Clk |

Sistemska ura |

|

Vnos |

Inter-PFU signal |

Fcin |

Hitro nošenje vvoz |

|

Izhod |

Podatkovni signali |

F0, f1 |

LUT4 izhodni register obvodni signali |

|

Izhod |

Podatkovni signali |

Q0, Q1 |

Registrirajte izhode |

|

Izhod |

Podatkovni signali |

Ofx0 |

Izhod LUT5 MUX |

|

Izhod |

Podatkovni signali |

Ofx1 |

Izhod LUT6, LUT7, LUT8 2 MUX, odvisno od rezine |

|

Izhod |

Inter-PFU signal |

Fco |

Za desno večino PFU hitro prevozno verižno izhod¹ « |

Specifikacije LFEC3E-3Q208C

|

Tip |

Parameter |

|

Proizvajalec |

Rešetki polprevodnik |

|

Napetost - dovod |

1.14V ~ 1.26V |

|

Skupni ovnovski koščki |

56.320 |

|

Paket dobaviteljskih naprav |

208-PQFP (28x28) |

|

Serija |

Ec |

|

Paket / ohišje |

208-BFQFP |

|

Paket |

Pladenj |

|

Delovna temperatura |

0 ° C ~ 85 ° C (TJ) |

|

Število logičnih elementov/celic |

3.100 |

|

Število V/I. |

145 |

|

Vrsta pritrditve |

Površinski nosilec |

|

Številka osnovnega izdelka |

LFEC3 |

LFEC3E-3Q208C aplikacije

1. vgrajeni krmilni sistemi

LFEC3E-3Q208C je primeren za vgrajene krmilnike v napravah, industrijski avtomatizaciji in IoT prehodih.Njegova zmerna logična gostota in nizkocenovni dizajn omogočata nadomeščanje logike s fiksno funkcijo s programirljivo prilagodljivostjo.To olajša nadgradnjo sistemov ali prilagajanje razvijajočim se standardom brez preoblikovanja strojne opreme.

2. Povezovanje pomnilnika DDR

Z vgrajeno podporo za pomnilnik DDR400 lahko naprava upravlja medsebojno delovanje podatkov, sečnjo ali začasno shranjevanje v aplikacijah.Ta funkcija je uporabna v sistemih, kjer je zunanja hitrost pomnilnika pomembna, vendar popolna uspešnost FPGA višjega cenovnega razreda ni potrebna.Mnogi imajo koristi od ravnotežja hitrosti, stroškov in učinkovitosti pomnilnika.

3. Preoblikovanje in pretvorbo protokolov

Zahvaljujoč široki podpori za standarde I/O, kot so LVCMOS, LVTTL, LVDS, PCI in SSTL, je FPGA učinkovit pri premostitvi različnih digitalnih vmesnikov.Lahko je konfiguriran za prevajanje signalov med podsistemi, zaradi česar je dragocen v mešani-tehnoloških modelih.Ta prilagodljivost pomaga podaljšati življenjsko dobo obstoječe strojne opreme, tako da omogoča združljivost z novimi komponentami.

4. industrijske in infrastrukturne aplikacije

Naprava lahko služi tudi v stroškovno občutljivi industrijski in infrastrukturni opremi, kjer zadostujeta zanesljivost in zmerna zmogljivost.Njegova podpora za mejno skeniranje, odpravljanje napak na čipu in delovanje z nizko močjo omogočajo idealno za sisteme, ki zahtevajo učinkovitost in enostavno vzdrževanje.Tipične vloge vključujejo kontrolne enote, vmesniške module in sisteme za spremljanje.

Podobni deli LFEC3E-3Q208C

|

Specifikacija |

LFEC3E-3Q208C |

LFEC3E-3Q208I |

LFEC3E-3QN208C |

LFEC3E-4Q208C |

LFEC1E-3Q208C

|

LFEC6E-3Q208C

|

|

Logični elementi (LUTS) |

~ 3,1k |

~ 3,1k |

~ 3,1k |

~ 3,1k |

~ 1,5k |

~ 6,1k |

|

Logični bloki |

384 |

384 |

384 |

384 |

192 |

768 |

|

Vgrajeni blok RAM (EBR) |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 18 kb |

~ 92 kb |

|

Največja delovna frekvenca |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 300 MHz |

~ 340 MHz |

|

Štetje I/O. |

145 |

145 |

145 |

145 |

112 |

145 |

|

Paket |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

|

Jedrna napetost |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

|

Temperaturno območje |

0 ° C do +70 ° C. |

–40 ° C do +85 ° C. |

0 ° C do +70 ° C. |

0 ° C do +70 ° C. |

0 ° C do +70 ° C. |

0 ° C do +70 ° C. |

|

Vrsta skladnosti / paketa |

Standardno |

Industrijsko |

Brez svinca (QN) |

Varianta (q) |

Standardno |

Standardno |

|

Aplikacija |

Srednja gostota, splošno namena |

Enako kot LFEC3E, vendar industrijska uporaba |

Enako kot LFEC3E, vendar skladen s paketom |

Ista družina, enostavna migracija |

Možnost stroškov z nizko gostoto |

Nadgradnja višje gostote |

Koraki programiranja LFEC3E-3Q208C

Preden začnete s programiranjem programiranja LFEC3E-3Q208C, je pomembno, da pripravite prava orodja in razumete pretok zasnove do konfiguracije naprave.Vsak korak je zasnovan na prejšnjem, zato bo skrbna pozornost zagotovila nemoten postopek programiranja.

1. Pripravite programsko opremo in programsko opremo

Začnete z nameščanjem rešetkastega programerja Diamond ali sistema ISPVM, ki so uradna orodja za to FPGA.Nato nastavite programski kabel JTAG, kot je HW-USBN-2B, in se prepričajte, da so vozniki pravilno nameščeni.Ta korak zagotavlja, da je vaš računalnik pripravljen za komunikacijo s ciljno napravo brez napak pri povezavi.

2. Izvedite svoj dizajn v razvojni programski opremi

Nato ustvarite nov projekt v Lattice Diamond in za svojo ciljno napravo izberite LFEC3E-3Q208C.Nato dodate svoje izvorne datoteke Verilog ali VHDL, uporabite naloge PIN in določite morebitne omejitve.Ko to storite, sintetizirate zasnovo, izvedete mesto in na koncu in na koncu ustvarite datoteko Bitstream (.bit ali .Jed), ki bo uporabljena za programiranje.

3. Nastavite desko in povezave

Zdaj priključite kabel JTAG na svojo ploščo FPGA in se prepričajte, da je ozemljitvena povezava varna, preden pritrdite signalne črte.Prepričajte se, da so vlečni in spustni upori pravilno na mestu, zlasti na TCK in linijah z odprtim odtokom.Če ima vaša plošča dodatne kontrolne zatiče, kot sta Erase ali Ispen, jih morate pravilno konfigurirati, da preprečite naključne ponastavitve med programiranjem.

4. Program naprave

S strojno opremo zaženite orodje za programiranje in izberite povezan kabel.Naložite ustvarjeno datoteko Bitstream in izberite ustrezen način, običajno JTAG, odvisno od vaše nastavitve.Zaženite postopek programiranja in orodje bo konfiguriralo FPGA, hkrati pa preverite, ali so bili podatki pravilno napisani.

5. Preverite in odpravljate napako konfiguracije

Po programiranju preverite končane ali init zatiče na svoji plošči, da potrdite, da je FPGA uspešno konfigurirana.Če je potrebno, uporabite analizator logike isptracy ali funkcije mejnega skeniranja, da preizkusite funkcionalnost in preverite vedenje signala.Cikel oblikovanja in programiranja lahko ponovite vsakič, ko so potrebne spremembe, in tako zagotovite, da je vaš projekt korak za korakom izpopolnjen.

Prednosti in slabosti LFEC3E-3Q208C

Prednosti

• Nizka poraba energije, primerna za energijsko občutljive modele

• Stroškovno učinkovit v primerjavi z višjimi FPGA

• Preprosta orodja z lažjo krivuljo učenja

• Polje, ki je mogoče konfigurirati za posodobitve po uvajanju

• Kompaktni paket z dobrim ravnovesjem virov

Slabosti

• Omejena zmogljivost v primerjavi z večjimi FPGA

• Nižja logika in zmogljivost pomnilnika kot naprave višjega cenovnega razreda

• Manj tretjih oseb IP in podpora ekosistema

• Toolchain nima naprednih funkcij večjih prodajalcev

• Ni primeren za vmesnike ultra visoke hitrosti

LFEC3E-3Q208C dimenzije embalaže

|

Tip |

Parameter |

|

Vrsta paketa |

208-PQFP (Plastic Quad Flat paket) |

|

Velikost telesa |

28 mm × 28 mm |

|

Nagib |

0,5 mm |

|

Višina paketa (max) |

~ 3,4 mm |

|

Število svinca |

208 zatičev |

|

Slog paketa |

Gule-krilci (Quad) |

|

Vrsta pritrditve |

Površinski nosilec |

|

Koda primera |

BFQFP-208 |

|

Paket dobaviteljev |

Pladenj |

Proizvajalec LFEC3E-3Q208C

LFEC3E-3Q208C izdeluje Lattice Semiconductor Corporation , ameriško podjetje s sedežem v Hillsboroju v Oregonu.Lattice, ustanovljena leta 1983, je specializirana za razvoj nizkih moči, stroškovno učinkovite poljske vrat (FPGA) in z njimi povezane rešitve.Podjetje se osredotoča na omogočanje aplikacij na področju komunikacij, računalništva, potrošniške elektronike, industrijskega in avtomobilskega trga.Znana po svoji inovaciji v energetsko učinkovitih programirnih napravah se je rešetka uveljavila kot ključni akter v industriji FPGA, zlasti za modele, ki zahtevajo kompaktne faktorje, zmanjšano porabo energije in visoko zanesljivost.

Zaključek

LFEC3E-3Q208C ponuja dobro mešanico nizkih stroškov, nizke porabe energije ter dovolj logike in pomnilnika za projekte srednjega razreda.Podpira številne standarde V/I, ima vgrajen RAM in PLL in lahko deluje s pomnilnikom DDR400, zaradi česar je uporabna za nadzor, vmesnik in industrijske naloge.Programiranje je preprosto z rešetkastimi orodji, dodatne funkcije za odpravljanje napak pa pomagajo pri testiranju.Čeprav se ne more ujemati s hitrostjo in zmogljivostjo večjih FPGA, je zanesljiva izbira za modele, ki potrebujejo fleksibilnost, učinkovitost in cenovno ugodne zmogljivosti.

PDF podatkovnega lista

LFEC3E-3Q208C podatkovni listi:

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Pogosto zastavljena vprašanja [FAQ]

1. Ali LFEC3E-3Q208C podpira visoke hitrostne vmesnike, kot sta PCIe ali Gigabit Ethernet?

Št. LFEC3E-3Q208C je zasnovan za običajne in stroškovno občutljive aplikacije, zato ne vključuje domačih serijskih oddajnikov visoke hitrosti.Namesto tega se osredotoča na vzporedne vmesnike in podporo pomnilnika DDR.

2. Ali se lahko LFEC3E-3Q208C po uvajanju reprogramira?

DA.Kot FPGA je LFEC3E-3Q208C v celoti ponovno konfiguriran, kar omogoča posodobitve in modifikacije oblikovanja tudi po uvajanju.Ta prilagodljivost zmanjšuje dolgoročne stroške vzdrževanja in razširja življenjske cikle izdelka.

3. Kako se LFEC3E-3Q208C loti odpravljanja napak in testiranja?

Naprava integrira mejne skeniranje (IEEE 1149.1), analizo logike na čipu (isptracy) in podporo SPI Boot Flash.Ta vgrajena orodja poenostavijo odpravljanje napak in zmanjšujejo potrebo po zunanji strojni opremi.

4. Ali lahko LFEC3E-3Q208C podaljša življenjsko dobo starejših strojnih sistemov?

Da, zahvaljujoč široki zmogljivosti za združljivost I/O in premostitve protokola, lahko povezuje starejše sisteme z novejšimi komponentami in podjetjem pomaga razširiti uporabnost obstoječe strojne opreme.

5. Katera programska orodja so potrebna za LFEC3E-3Q208C?

Programirano je s pomočjo Diamond programerja ali sistema ISPVM.Ta orodja podpirajo vnos oblikovanja, generacijo bitstream in konfiguracijo naprav, zaradi česar je potek dela racionaliziran.

AD73311LARS: podatkovni list, funkcije, pinout in vodnik za programiranje

na 2025/08/28

EPM1270F256C4N MAX II CPLD Pregled: Funkcije, specifikacije in aplikacije

na 2025/08/28

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/17 147721

-

USB-C pinout in funkcije

na 2000/04/17 111783

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/17 111328

-

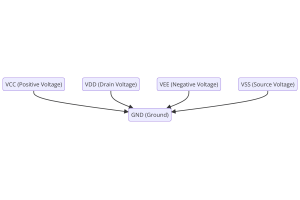

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/17 83649

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79354

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66806

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 62967

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 62859

-

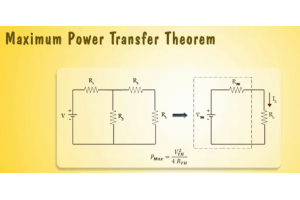

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54049

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52032