Evolucija in vpliv arhitekture RISC v sodobnem računalništvu

Ta priročnik raziskuje zmanjšano računalništvo z navodili (RISC), ključni pristop pri mikroprocesorskem oblikovanju, ki s poenostavitvijo navodil povečuje hitrost in učinkovitost.RISC, ki so ga prvič razvili v osemdesetih letih prejšnjega stoletja, navdihnjeni s prejšnjimi koncepti MIPS Mainframe, je pokazal, da bi lahko uporaba manj navodil močno izboljšala delovanje.Pod vodstvom Johna Cockeja na IBM -u je ta dizajn poenostavil operacije procesorja za hitrejšo izvedbo v primerjavi s kompleksnimi sistemi.Danes načela RISC poganjajo številne sodobne mikroprocesorje, ki spodbujajo k učinkovitejšemu računalništvu.Članek zajema zgodovino RISC, temeljne ideje, trenutne uporabe in trajni vpliv na tehnologijo.Katalog

Izboljšane perspektive računalniške arhitekture

Zmanjšano računalniško nastavitev navodil (RISC) in kompleksno nastavitev računalništva (CISC) predstavljata dva kontrastna pristopa k računalniški arhitekturi, vsak z različnimi evolucijskimi potmi.RISC-ov minimalistični nabor navodil se osredotoča na optimizacijo pogosto uporabljenih ukazov z učinkovitimi strategijami prevajalnika, ki omogoča hitro izvajanje in zmanjšano porabo pomnilnika, ki so postale ključni igralec v visokozmogljivih sistemih, kot so Compaq's Alpha, HP-jev PA-RISC, IBM-ov PowerPC, MIPS, MIPS, MIPS, MIPSin Sun's Sparc.V nasprotju s tem se CISC opira na zapletene zasnove strojne opreme, da doseže pridobivanje zmogljivosti z bolj zapletenimi navodili.RISC-ova preprostost, ki je podkrepljena z napredkom v pomnilniških tehnologijah in izvajanju enokoletnih navodil, prinaša hitro, učinkovito obdelavo v okolju z veliko povpraševanjem, kjer je potrebna zmanjšana zamuda.Praktične inovacije, kot so rafinirani nadzor strojne opreme in prefinjene tehnike prevajalnika, zagotavljajo, da RISC ostane pomemben pri ravnanju s sodobnimi računalniškimi izzivi.V današnji tehnološki pokrajini, ki se hitro razvija, se je RISC-jeva prilagodljivost in učinkovitost obdelave dokazala v podatkovno intenzivnih operacijah, ki ponujajo robustne zmogljivosti strežnika in agile razvojne cikle, ki ustrezajo naraščajočim zahtevam sodobnega računalništva.Ko se arhitektura še naprej razvija, RISC -ova mešanica preprostosti in razširljivosti krepi njegov trajni pomen in transformativni potencial v različnih panogah.

Razvrstitev v sodobnem računalništvu

Napredni poučni cevovodi in umetnost učinkovitosti obdelave

RISC Architecture sprejmejo nabor prefinjenih pristopov k povečanju računske učinkovitosti in s tem subtilno obravnava prirojeno željo po hitrosti in odzivnosti.Z uporabo večstopenjskih navodnih cevovodov ti sistemi spretno upravljajo hkratno obdelavo več navodil.Po drugi strani zmanjšujejo izpadanje CPU -ja in povečajo celotno prepustnost.Prednostno uporabo preprostih, pogosto uporabljenih ukazov, poleg paradigme obremenitve in shranjevanja, ki omejuje interakcije pomnilnika, povzroči optimizirano uporabo registra.V vsakdanjem okolju, kjer lahko hitro izvedbo bistveno vpliva na vaše izkušnje in zadovoljstvo, te strategije sijejo.

Navigacija po hitrostnih izzivih s prefinjenimi tehnikami izvajanja

Za reševanje morebitnih ovir za hitrost zaradi neskladja za razvejanje in hitrost pomnilnika sistemi RISC inteligentno izkoriščajo špekulativno izvedbo in obdelavo zunaj reda.Te strategije omogočajo procesorju, da predvideva in se pripravi na različne poti pouka, kar na koncu zagotavlja nemoteno izvedbo v zapletenih situacijah.Razumevanje teh metodologij ponuja globok vpogled v načela optimizacije, ki oblikujejo današnje vrhunske modele procesorjev, kar subtilno odraža pot industrije do pametnejših in bolj intuitivnih računalniških rešitev.

Dviganje pasovne širine s strateškimi arhitekturami predpomnilnika

Izboljšave za arhitekturo predpomnilnika igrajo vlogo pri povečanju pasovne širine, kar olajša učinkovito in tekočino poučevanja v CPU.Te strategije smiselno zmanjšujejo zamude, kar omogoča hiter dostop do pogosto uporabljenih podatkov, kar je nujno za hitro obdelavo v različnih aplikacijah.V akciji takšne metodologije vodijo do večje odzivnosti in uspešnosti sistema, ki izpolnjujejo zahteve industrij, kjer je visokozmogljivo računalništvo več kot le udobje.

Dinamika primerjalne zmogljivosti z modeli CISC

S temi naprednimi metodologijami RISC procesorji iz podjetij, kot so Intel, AMD in Cyrix, dosegajo meritve uspešnosti, ki zasenčijo tradicionalne modele CISC.Ta izrazita uspešnost je opažena pri strokovnem ravnanju s kompleksnimi nalogami RISC, zaradi česar so ti procesorji vrhunska izbira v sektorjih, kjer je zaželena mogočna procesna moč.Ta vpogled se usklajuje s širšimi tehnološkimi premiki in kaže na neusmiljeno prizadevanje za inovacije, kar poganja polprevodniško industrijo k razširljivim procesorskim rešitvam, ki ustrezajo nenehno razvijajoči se žeji po moči in učinkovitosti.

Značilnosti arhitekture RISC

Racionalizirani niz navodil

RISC Architecture se vrti okoli svojega namenoma minimalnega nabora navodil, ki vsebuje manj kot 128 navodil.Ta navodila so opredeljena z njihovimi jasnimi načini naslova in dosledno obliko.S tem, ko se osredotočajo na zmanjšanje, sistemi RISC aktivno povečujejo hitrost s tehnikami, kot so navodila za cevovod in pristop obremenitve/trgovine, kar omogoča, da se naloge končajo v samo enem strojnem ciklu.Ta preprost pristop ne samo pospešuje izvajanje nalog, ampak tudi olajša postopek dekodiranja navodil, kar ustreza sodobnim računalniškim zahtevam, ki nastanejo za učinkovitost in hitrost.

Neposreden nadzor za izboljšano izvedbo

V arhitekturi RISC trdožičeni nadzorni mehanizmi pogosto imajo prednost pred mikroprogramiranjem.Ta izbira poenostavlja oblikovanje procesorjev in poudarja hitro, zanesljivo delovanje.Z zaoblikovanjem posredniških kontrolnih korakov procesorji delujejo na bolj neposreden in učinkovit način, ki je prikimaval nestrpnosti z zamudami in željo po neposrednosti.Ta metodologija omogoča ostrejši poudarek na procesih rafiniranja in doseganju povišane zmogljivosti, kar kaže na praktični vpliv zmanjšanja zamude odločitve na sistemske zmogljivosti.

Obsežno shranjevanje in ravnanje s podatki

Obile registrirane banke v sistemih RISC okrepijo učinkovitost ravnanja s podatki.Zmanjšajo pogoste dostop do pomnilnika, ki služijo kot hitro shranjevanje in ublažitev upočasnitve, ki jo povzročajo zamude pomnilnika.Večje zmogljivosti za shranjevanje registra olajšajo takojšnjo obdelavo podatkov, kar povečuje skupno hitrost sistema.Ta osredotočenost na notranje upravljanje podatkov odmeva z natančnostjo za brezhibno in brez težav, ki podčrtajo zavezanost RISC-a k visoki pretočni pretoki, hkrati pa ohranja rafinirano kompleksnost strojne opreme.

Poudarek na obdelavi spretnosti

Strateške izbire oblikovanja, vgrajene v RISC, so izdelane za povečanje učinkovitosti, hkrati pa ohranjajo nizko kompleksnost strojne opreme.To ne odraža le teoretične ambicije, ampak pragmatično opazovanje v mnogih aplikacijah, kjer racionalizirane operacije prinašajo hitro odzivne računalniške izkušnje.Z prednostno nalogo pretoka in preprostosti RISC spretno orkestrira računske vire za reševanje prefinjenih procesov s pozo.Ta namen krepi vlogo RISC -a v sodobnih računalniških in vpliva na razvojne usmeritve procesorjev, kar potrjuje arhitekturni rob, ki ga zagotavljajo kompaktni nabori pouka pri doseganju impresivnih zmogljivosti z premišljenim dizajnom.

Prednost RISC Architecture

Racionalizirano oblikovanje in integracija

RISC Architecture izstopa s svojimi različnimi prednosti, zlasti z združljivostjo z zelo veliko tehnologijo integracije (VLSI).Njegov preprost dizajn vodi do zmanjšanih velikosti čipov in izboljšane zanesljivosti z zmanjšanjem napak v oblikovanju.Pri oblikovanju procesorjev se odločitev za manj zapleten pristop pogosto povzroči učinkovitejše proizvodnje in krajše časovne roke razvoja.To načelo se ujema z vpogledi, ki negujejo odpravljanje nepotrebnih zapletenosti za doseganje najvišje funkcionalnosti.

Povečana hitrost in stroškovno učinkovitost

Učinkovite kontrolne enote znotraj procesorjev RISC spodbujajo hitrejše hitrosti obdelave poleg zmanjšanih stroškov oblikovanja.Ta metodologija ponuja jasne in neposredne poti za izvajanje navodil, ki prispevajo k učinkoviti porabi energije in visoki operativni produktivnosti.Takšne izboljšave pri obdelavi hitrosti in varčevanja z energijo se brezhibno usklajujejo s potrebami industrije po stroškovno učinkovitih rešitvah, kar zagotavlja taktično prednost pri inovacijah strojne opreme.

Združljivost z jeziki na visoki ravni

RISC-ova oblikovalska strategija podpira programske jezike na visoki ravni in ne z montažnimi jeziki, v skladu s sodobnimi razvojnimi trendi.Učinkovito obravnava vztrajni izziv, znan kot "programska kriza."Ta poravnava poenostavlja odpravljanje napak in vzdrževanje, kar ustvarja okolje, ki spodbuja inovacije in hitro prototipiranje, brez omejitev programiranja na nizki ravni.Številni razvijalci programske opreme cenijo zanesljive rezultate uspešnosti RISC Architecture, ki racionalizira njihova prizadevanja in povečuje učinkovitost.

Integracija programske opreme in racionalizirana optimizacija

Eden od dejavnikov uspeha arhitekture RISC je njena brezhibna integracija z obstoječimi programskimi sistemi, ki jo olajšajo s ponovnim postopkom, ki so združljivost stresa.Ta funkcija močno izboljša izkušnjo, saj programerjem zagotavlja dosleden niz navodil, ki racionalizira optimizacijo kode in predvidljivost.Strokovnjaki za programsko industrijo cenijo jasnost in enakomernost, ki jo prinaša v razvojni proces, kar zmanjšuje neskladnosti med različnimi konfiguracijami strojne in programske opreme.

Izzivi in prihodnja obzorja

Notranje zapletenosti

RISC Architecture, pohvaljena zaradi učinkovitega in preprostega dizajna, se sooča s povezanimi zapletenostmi.Pomembno vprašanje je povečano povpraševanje po spominu zaradi dolžine sestavljenih navodil, ki lahko vzbudijo tesnobo zaradi zmogljivosti skladiščenja in iskanja podatkov.Prisotnost obsežnih naborov registra dodaja nalogo z zapletenim reševanjem shem in zahteva premišljene rešitve.Omejitve enosmernih navodil uvajajo izzive pri ravnanju s 32-bitnim naslovom, ki pogosto zahteva dvopisna navodila za učinkovito upravljanje podatkov.Doseganje ravnotežja med učinkovito uporabo pomnilnika in optimalno uspešnostjo zahteva ustvarjalno reševanje problemov in natančne prilagoditve.

Evolucija in uskladitev

Kljub tem prirojenim izzivom je potencial RISC okrepljen s svojo sposobnostjo prilagajanja in razvoja.Neprestana mešanica elementov RISC in CISC kaže na hibridni model, ki uporablja najboljše iz obeh svetov, kar kaže na zadružni odnos in ne na tekmovalno.Zlasti ima vlogo pojav SuperScalar in Superpipenirane arhitekture, saj močno izboljšujejo uspešnost RISC.Ti napredki povečujejo zmogljivosti procesorja, saj omogočajo obdelavo več navodil hkrati v vsakem ciklu, kar je sposobnost, ki se v okoljih z intenzivnimi računskimi zahtevami zdi zelo ugodna.

Trajni vpliv na tehnološko pokrajino

Prilagodljiva rast RISC zagotavlja njegov nenehni pomen in vpliv pri oblikovanju prihodnjih procesorjev in obsežnega računalniškega področja.Ko zahteve po računalniški moči in učinkovitosti rastejo, RISC stoji pripravljen spodbuditi tehnološki napredek.Njegova prirojena učinkovitost ponuja trajno vrednost v različnih aplikacijah, od vgrajenih sistemov do višjega cenovnega računalniškega rešitev.Praktična uporaba RISC v sistemih poudarja njegovo vlogo v scenarijih, kjer je pomemben predvidljiv čas izvedbe.Posledično RISC še naprej služi ne le kot temeljna tehnologija, ampak kot odlična komponenta, ki navdihuje naslednji val inovacij v računalniški arhitekturi.

Možnosti tehnologije RISC

RISC (zmanjšan računalnik z navodili) se osredotoča na poenostavitev oblikovanja procesorjev, da pospeši izvajanje navodil, v nasprotju s CISC (kompleksni računalnik za navodila), ki daje prednost enostavnosti programiranja s kompleksnejšimi navodili.Sodobni procesorji pogosto združujejo oba pristopa, da dosežejo boljšo zmogljivost.Na primer, čipi, kot sta Intel's 80486 in Motorola 68040, vključujejo tehnike RISC, da skrajšajo čas pouka na manj kot 2 cikla, medtem ko Fairchild Clipper dosega hitrost do 33 MIP -jev s kombiniranjem elementov RISC in CISC.Novi napredki, kot so SuperScalar in Superpipening Technologies, še naprej spodbujajo delovanje RISC, tako da omogočajo hkrati obdelavo več navodil.Procesorji, kot je IBM -ov RS/6000, lahko s temi metodami izvedejo do šest navodil na cikel.Vendar pa drugi napovedujejo, da se bodo prihodnji dobički manj osredotočili na surovo hitrost in bolj na izboljšanje učinkovitosti predpomnilnika, prevajalnikov in večprocesorskih sistemov.

O nas

ALLELCO LIMITED

Preberi več

Hitro povpraševanje

Prosimo, pošljite poizvedbo, takoj bomo odgovorili.

Celovit vodnik za testne steze: Orodja in tehnike za preverjanje digitalnega sistema

na 2025/01/7

Obsežen vodnik za osciloskope za analizo signala

na 2025/01/7

Priljubljene objave

-

Kompleksni nastavitveni računalniki: Kako so spremenili računalništvo?

na 8000/04/18 147751

-

USB-C pinout in funkcije

na 2000/04/18 111924

-

Uporaba Xilinx Unified Simulacijske primitive: Obsežen vodnik za oblikovanje in simulacijo FPGA

na 1600/04/18 111349

-

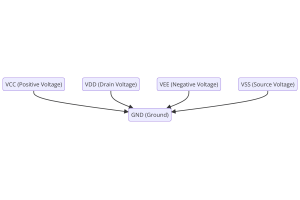

Napajalne napetosti v elektroniki: pomen VCC, VDD, VEE, VSS in GND

na 0400/04/18 83714

-

Vodnik priključkov RJ45: pinout, ožičenje, vrste kablov in uporabe

na 1970/01/1 79502

-

Ultimate Guide za žičnice barvnih kod v sodobnih električnih sistemih

Način, kako naši električni sistemi uporabljajo barve, ni samo za videz.Vsaka barva žice zdaj označuje določeno funkcijo, kar olajša pravilno prepoznavanje in ravnanje z električnimi komponentami m...na 1970/01/1 66872

-

Faktor kakovosti (q): enačbe in aplikacije

Faktor kakovosti ali "Q" je pomemben pri preverjanju, kako dobro induktorji in resonatorji delujejo v elektronskih sistemih, ki uporabljajo radijske frekvence (RF).'Q' meri, kako dobro vezje minimi...na 1970/01/1 63005

-

Vodnik za čiščenje ventila: funkcija, simptomi, testiranje in zamenjava za optimalno delovanje motorja

Čistilni ventil je ključni del sistema avtomobila, ki pomaga ohranjati čist zrak z upravljanjem hlapov goriva, preden lahko pobegnejo v ozračje.To ne samo pomaga okolju z zmanjšanjem onesnaževanja,...na 1970/01/1 62955

-

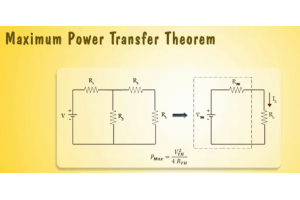

Doseganje največjih zmogljivosti z največjim teoremom o prenosu energije

Teorem največjega prenosa moči pojasnjuje, kako energija iz vira, na primer baterija ali generator, teče v povezano obremenitev.Prikaže natančen pogoj, kjer obremenitev prejme največ moči.Ta članek...na 1970/01/1 54078

-

A23 Specifikacije baterije in združljivost

Akumulator A23 je majhna baterija v obliki valja z visoko napetostjo.Imenovan tudi 23A, 23AE ali MN21, deluje pri 12 voltih in veliko višji od baterij AA ali AAA.Njegova posebna zasnova je...na 1970/01/1 52092